# RAMROD: AN EXPERIMENTAL MULTI-MICROPROCESSOR

Alan Errol Rabinowitz

A Thesis Submitted to the Faculty of Engineering University of the Witwatersrand, Johannesburg, for the Degree of Doctor of Philosophy.

Johannesburg 1982.

This thesis is dedicated to the confidence memory of my leading mather

Anne Rabinowitz D.Y.A.

Who Separted on 27 Adm 9775.

## DECLARATION

I hereby declare that this thesis is my own work and that it has not previously been submitted for a degree at any other university.

alog memory Alan Errol Rabinowitz

23rd Day of December ,

1982

#### ABSTRACT

The computer architect of the 80's races an apparently intractable dilemma: Computer manufacturers have to contend with the soaring costs incurred in producing custom-made chips, and would prefer to use commercially-available, state-of-the art, large-scale integrated circuits. Product users, however demand highly reliable, realistically- priced systems which are nevertheless flexible enough to meet changing needs.

It is generally accepted that to be reliable and flexible a system should be conceptually simple and inherently fault-'.olerant. Further, accepting the necessity for maintenance, it becomes clear that the architecture should be totally modular both for hardware and for software.

This thesis is an attempt to reconcile these seemingly conflicting demands. An architecture is proposed, based on the frequently-used principle of closely-coupled multiprocessors, which avoides the pitfalls of over-complexity and too-heavy software dependance.

The proposed system is inherenty simple, making use of a single, high-speed time-division multiplexed bus to provide for communication between processors and memory. Software complexity is reduced by adopting a distributed, hardware-oriented operating system. Simplicity is enhanced by the use of a unified memory structure, whereby the user may freely allocate local or global memory, or a mixture of both.

Of importance is the use throughout of commercially-available, large- scale integrated ci.cuits. This is particularly relevant as the work was undertaken in isolation from the centres of research into custom-made microelectronics.

The author has developed the proposed system to prototype level. The prototype has been subjected to a series of performance evaluation tests, and the results obtained prove the viability of the technique adopted, and demonstrate its promise for the future.

The proposed system is inherenty simple, making use of a single, high-speed time-division multiplexed bus to provide for communication between processors and memory. Software complexity is reduced by adopting a distributed, hardware-oriented operating system. Simplicity is enhanced by the use of a unified memory structure, who teby the user may freely allocate local or global memory, or a mixture of both.

Of importance is the use throughout of commercially-available, large- scale integrated circuits. This is particularly relevant as the work was undertaken in isolation from the centres of research into custom-made microelectronics.

The author has developed the proposed system to prototype level. The prototype has been subjected to a series of performance evaluation tests , and the results obtained prove the viability of the technique adopted, and demonstrate its promise for the future.

#### ACKNOWLEDGEMENTS

The author wishes to express his sincere appreciation to the following people without whose help this thesis would not have been written.

Professor M.G. Rodd, his supervisor, Head of the Department of Electrical Engineering, University of the Witwatersrand, for his guidance, enthusiasm, interest and unselfish help in the writing of this thesis and advice on solution of technical problems and for the opportunity to be able to 'mirror' his thoughts.

Susan, his wife, for her patience, tolerance, enthus asm and encouragement throughout his 'career' as a student and her help in preparing the diagram.

Riva Rachel, Aviva Esther and Yona Mordechai, his children, who helped provide a reason for completing the work

Ralph and Anne Rabinowitz, his parents, for their material and moral support.

The technicians of the Department of Electrical Engineering for their contribution to the technical work and 'repairs' done to the project.

Gus Finucci and Johann Lambrechs, his colleagues, for their help through tight spots

Sue Rodd for the task of making the thesis legible and intelligable.

Finally the author wishes to thank the University of the Witwatersrand for the use of equipment, the CSIR for providing a grant for purchasing components, and Perseus for providing the author with a Research Fellowship.

#### GLOSSARY OF TERMS AND ABBREVIATIONS

CCU Computer Control Unit

EPROM Electrically Programmable Read Only Memory

TTL Transistor-Transistor Logic

CPA Central Processor Array

TDM Time-Division Multiplex

CPU Central Processing Unit

ECL Emitter Coupled Logic

ALU Arithmetic and Logic Unit

RAM Random Access Memory

MOS Metal Oxide Silicon

IC Integrated Circuit

DC Direct Current

VDU Visual Display Unit

ns nano-seconds

ma milli-amps 1/1000 amps

V Volts

nano 10\*\*-9

milli 10\*\*-3

micro 10\*\*-6

Kilo 10\*\*3

mbytes mega bytes

mega 10\*\*6

VLSI Very Large Scale Integrated

| CONT | ENTS      |                                       | PAGE  |  |  |

|------|-----------|---------------------------------------|-------|--|--|

|      | ABSTRAC   | · · · · · · · · · · · · · · · · · · · | (iii) |  |  |

|      |           | ACKNOWLEDGEMENTS                      |       |  |  |

|      | GLOSSAR   | Y OF TERMS AND ABBREVIATIONS          | (vii) |  |  |

|      | LIST OF   | GRAPHS, TABLES AND FIGURES            | (xii) |  |  |

|      | l INTRODU | CTION                                 | 1-1   |  |  |

|      | 1.1       | The Growing Demand for Computing      |       |  |  |

|      |           | Power                                 | 1-1   |  |  |

|      | 1.2       | Distributed Control                   | 1-3   |  |  |

|      | 1.3       | The Influence of Technology on        |       |  |  |

|      |           | Architecture                          | 1-15  |  |  |

|      | 1.4       | Software                              | 1-18  |  |  |

|      | 1.5       | Multiprocessors                       | 1-20  |  |  |

|      | 1.6       | Ramrod: a Multiprocessor Architec'ure | 1-26  |  |  |

|      | 1.7       | Conclusion                            | 1-27  |  |  |

| 2    | MULTIPRO  | OCESSORS                              | 2-1   |  |  |

|      | 2.1       | Multiprocessor Structures             | 2-1   |  |  |

|      | 2.2       | Interconection Strategies             | 2-4   |  |  |

|      | 2.3       | Shared Memory                         | 2-13  |  |  |

|      | 2.4       | Time-Division Multiplexed Bus         | 2-14  |  |  |

|      | 2.5       | Supervisor Control                    | 2-17  |  |  |

|      | 2.6       | An Overview of Ramrod                 | 2-17  |  |  |

|      | 2.7       | Conclusion                            | 2-20  |  |  |

| 3    | A REAL-T  | TIME OPERATING SYSTEM FOR Ramrod      | 3-1   |  |  |

| CONTENTS                                    | PAGE |

|---------------------------------------------|------|

| 3.1 The Role of an Operating System         | 3-1  |

| 3.2 Multiprocessor Operating Systems        |      |

| 3.3 The use of the Operating System         |      |

| in Ramrod 3                                 | 3-5  |

| 3.4 Basic Structure of the Operating        |      |

| System 3                                    | -7   |

| 3.5 Inter-Task Communications 3             | 12   |

| 3.6 User Task to Operating System           |      |

| Communication 3                             | -16  |

| 3.7 Conclusior 3                            | -16  |

| 4 HARDWARE STRUCTURE 4                      | -1   |

| 4.1 System Overview 4                       | -2   |

| 4.2 Basic Structure of Ramrod 4-            | -6   |

| 4.3 Physical Construction 4-                | -32  |

| 4.4 Conclusion 4-                           | -35  |

| 5 IMPLEMENTATION OF THE OPERATING SYSTEM 5- | -1   |

| 5.1 Operating System Kernel 5-              | - 2  |

| 5.2 Local Operating System 5-               | . 5  |

| 5.3 Conclusion 5-                           | 8    |

| 6 SOFTWARE STRUCTURE 6-                     | 1    |

| 6.1 Data Flow Approach6-                    | 2    |

| 6.2 Task Definition6-                       | 6    |

| 6.3 Inter-Task Communication                | 0    |

| CONTENTS  |                                      | PAGE |

|-----------|--------------------------------------|------|

| 6.4       | Conclusion                           | 6-15 |

| 7 EVALUAT | TION OF SYSTEM                       | 7-1  |

| 7.1       | Practical Limitations                | 7-2  |

| 7.2       | Factors Influencing the Relative     |      |

|           | Comparison                           | 7-4  |

| 7.3       | Program used in Relative Comparison. | 7-6  |

| 7.4       | Results                              | 7-8  |

| 7.5       | Conclusion                           | 7-12 |

| 8 CONCLUS | ION                                  | 8-1  |

| 8.1       | Uniqueness of Ramrod                 | 8-2  |

| 8.2       | Commercial Viability of Ramrod       | 8-4  |

| 8.3       | Critical Analysis of Ramrod          | 8-5  |

| 8.4       | Future Enhancements                  | 8-6  |

| 8.5       | Conclusion                           | £_7  |

| CONTENTS |                                        | PAGE |

|----------|----------------------------------------|------|

| APPEN    | DICES                                  |      |

| A        | Emitter Coupled Logic                  | A-1  |

| B        | Microprogramming Bit-Slice Technology. | B-1  |

| С        | The Modelling of a Circular Bus        | C-1  |

| D        | Currently available Multiprocessors    | D-1  |

| E        | Input/Output interfacing               | E-1  |

| Ę.       | The Exoslice Development System        | F-1  |

| G        | The Circuitry                          | G-1  |

| Н        | Marketing Costs of Ramrod              | H-1  |

| Ţ        | High Level Description of Programs     | I-1  |

| J        | Reliability                            | J-1  |

| REFER    | ENCES                                  | R-1  |

## Index to Figures, Tables and Circuit Diagrams

## Figures:

| No. | <u>Title</u>                               | PAG  |

|-----|--------------------------------------------|------|

|     |                                            |      |

| 2.1 | Typical Multiprocessor                     | 2-3  |

| 2.2 | Shared-bus                                 | 2-5  |

| 2.3 | Crossbar switch                            | 2-9  |

| 2.4 | Multiport Memory                           | 2-12 |

| 2.5 | System Diagram                             | 2-19 |

|     |                                            |      |

| 3.1 | Slave Processor to memory segement Pairing | 3-11 |

| 4.1 | Ramrod block Diagram                       | 4-3  |

| 4.2 | Timing on the Shared-Bus                   | 4-5  |

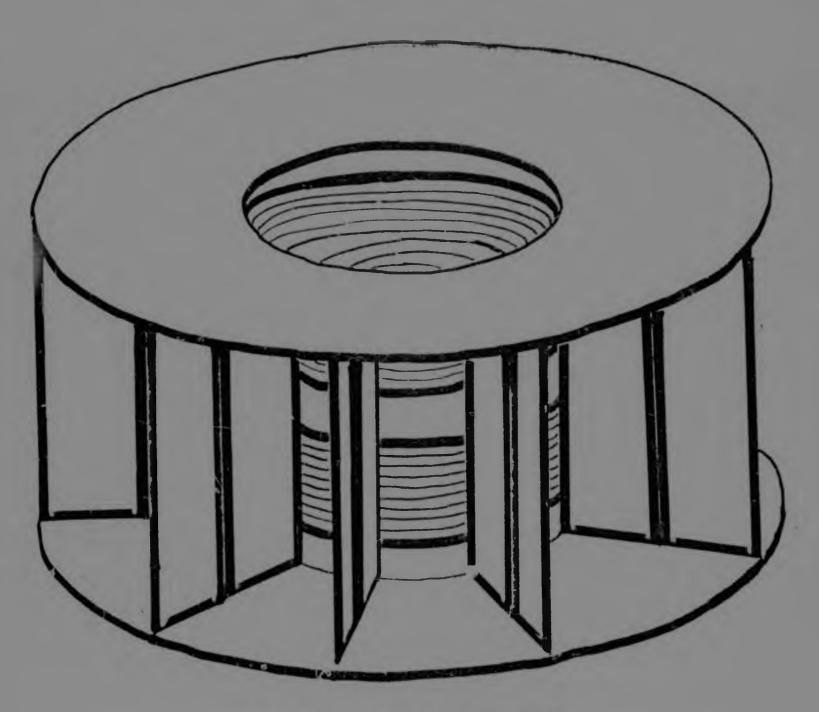

| 4.3 | Circular Construction                      | 4-14 |

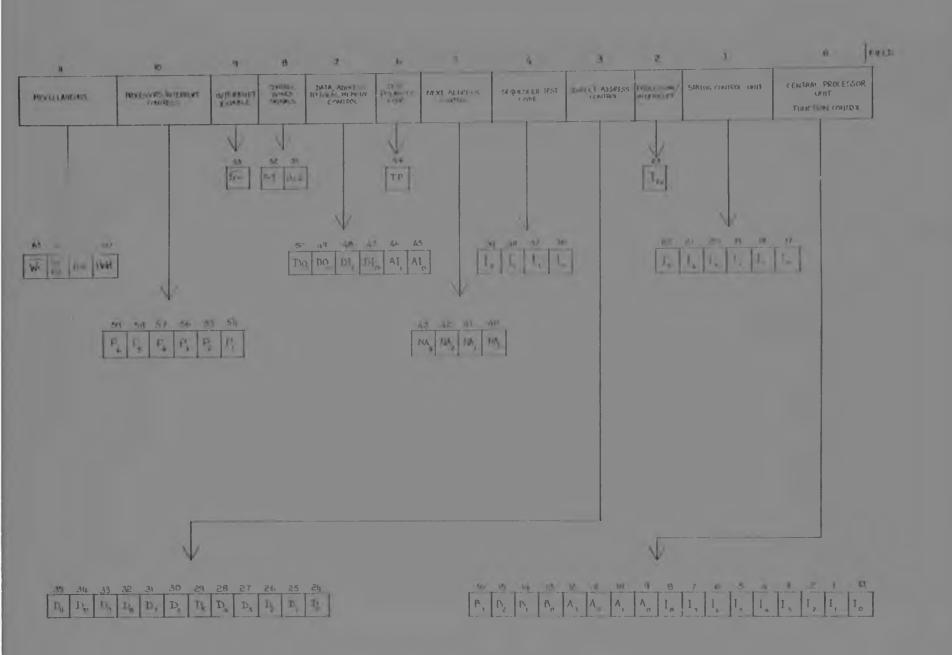

| 4.4 | Microinstruction format                    | 4-23 |

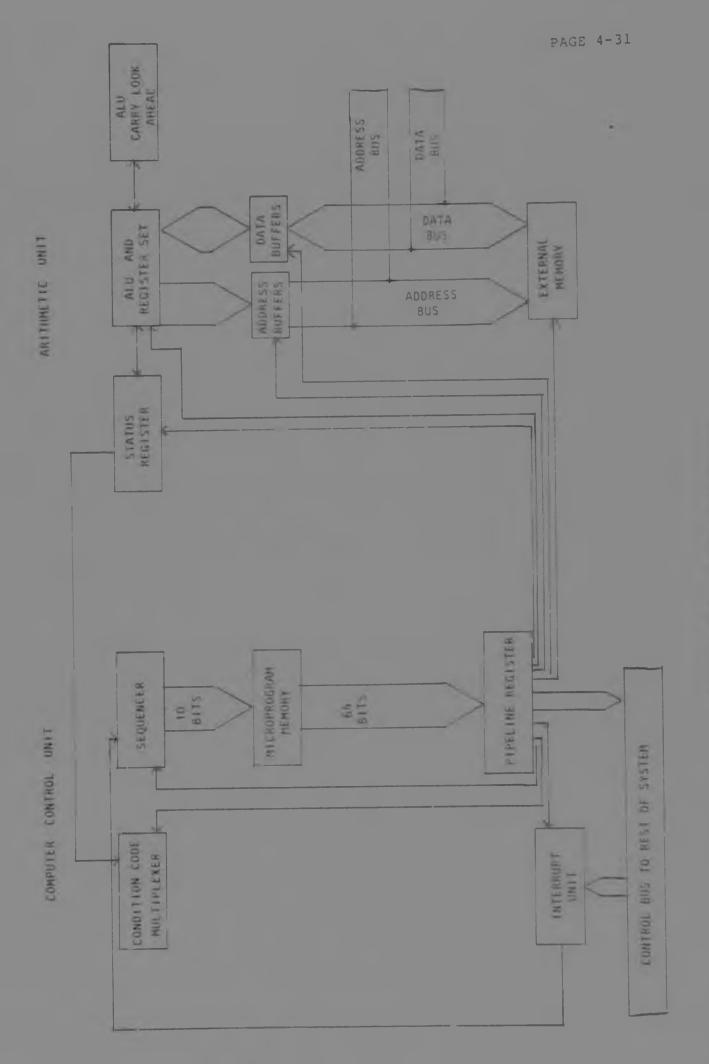

| 4.5 | Master Controller                          | 4-31 |

| 4.6 | View of Ramrod                             | 4-34 |

| 6.1 | Data flow Instructions                     | 6-5  |

| 7.1 | Operating System Sequence                  | 7-7  |

| 7.2 | Execution Sequence                         | 7-9  |

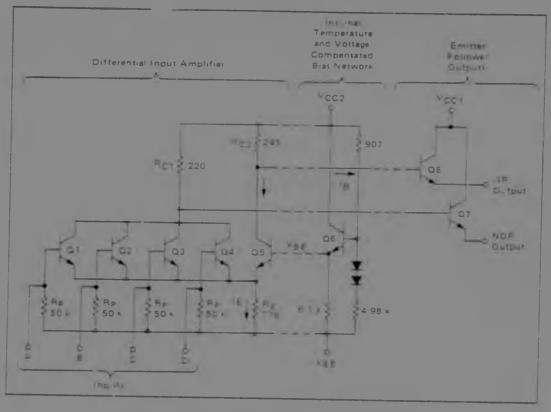

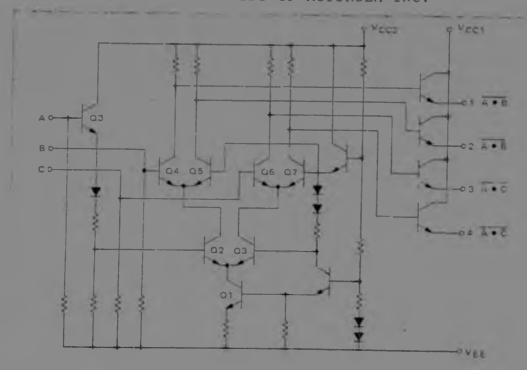

| A-1 | ECL Structure                              | A-4  |

| A-2 | Series Gating                              | A-4  |

| A-3 | Collector Dotting                          | A-5  |

| A-4 | 10804 latch                                | A-5  |

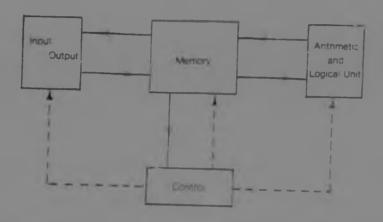

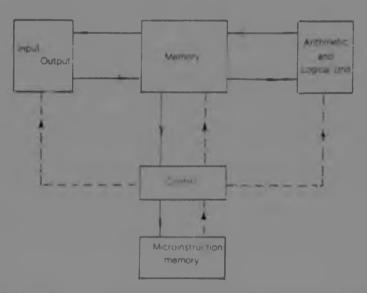

| B-1 | Conventional and Microprogrammed Computers | B-3  |

| B-2 | Typical Microprogrammed Computer           | B-5  |

| No.    | <u>Title</u>                         | PAGE |

|--------|--------------------------------------|------|

|        |                                      |      |

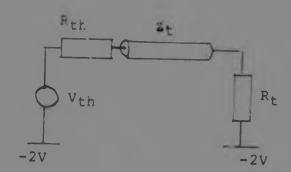

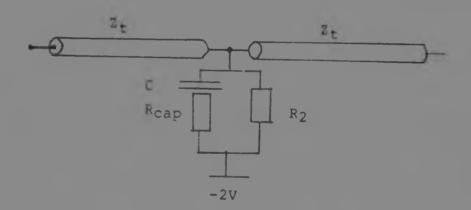

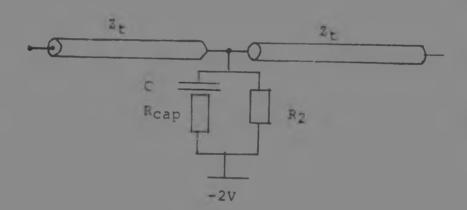

| C-1    | Thevenin Equivalent of Driving gate  | C+5  |

| C-2    | Capacitor Resistor network           | C-15 |

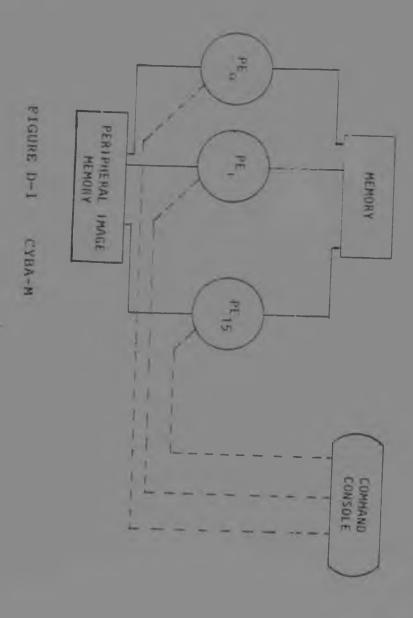

| D-1    | Cyba-M                               | D-2  |

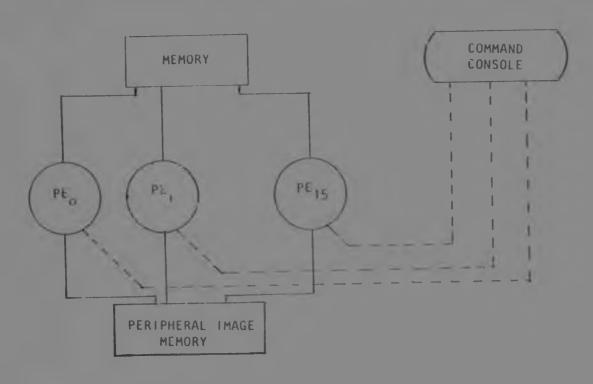

| D-2    | Siemens 4004/220, 230                | D-4  |

| D-3    | Siemens 201                          | D-6  |

| D-4    | Cmmp.                                | D-8  |

| D-5    | The Banyan Multi-Microcompter System | D-10 |

| D-6    | The Intel 432 System                 | D-13 |

| F-l    | Microinstruction execution steps     | F-7  |

| J-1    | Serial reliability                   | J-5  |

| J-2    | Parallel Reliability                 | J-5  |

| J-3    | Composite Reliability                | J-6  |

| J-4    | Ramrod's Reliability                 | J-6  |

|        |                                      |      |

| Circui | t Diagrams                           |      |

| No.    | <u>Title</u>                         |      |

| G-1    | Microprocessor Module                | G-2  |

| G-2    | ECL latch Module                     | G-4  |

| C-3    | Memory Module                        | G-6  |

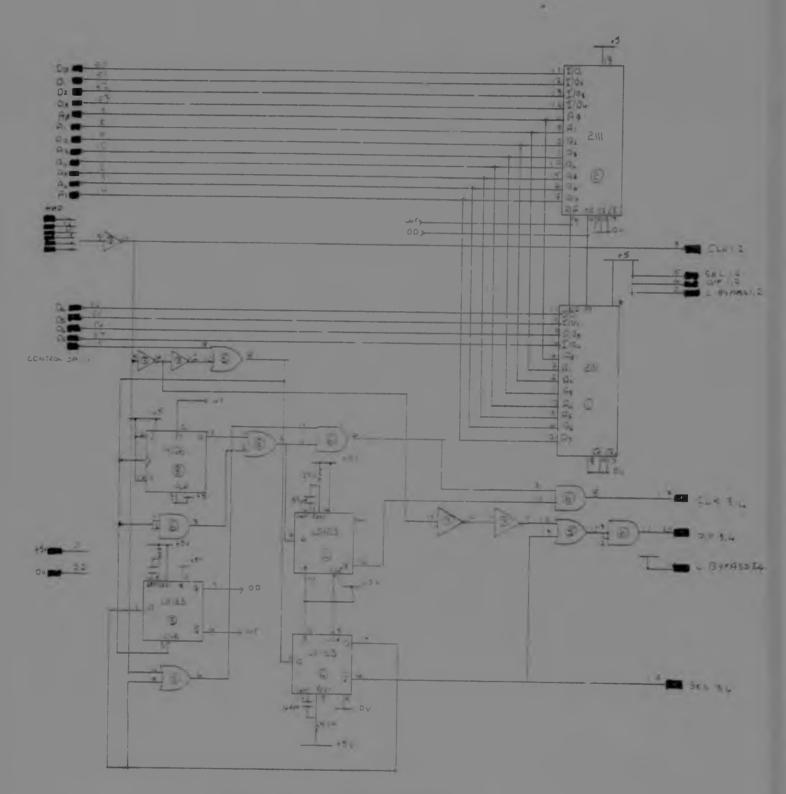

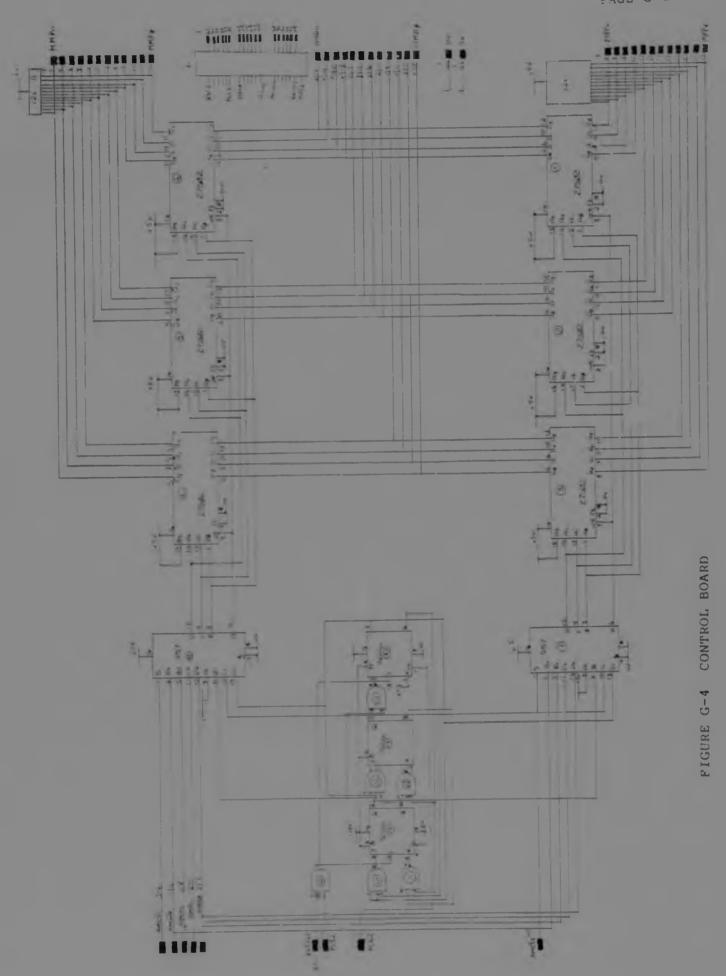

| G-4    | Control Board                        | G-8  |

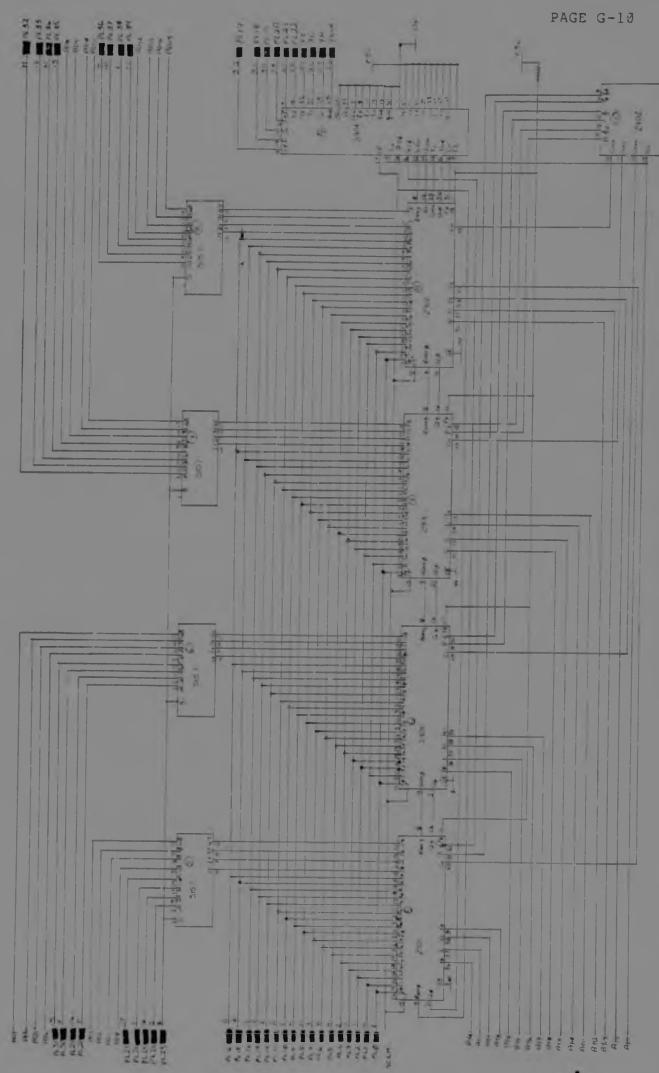

| G-5(a) | Central Processor Array              | G-10 |

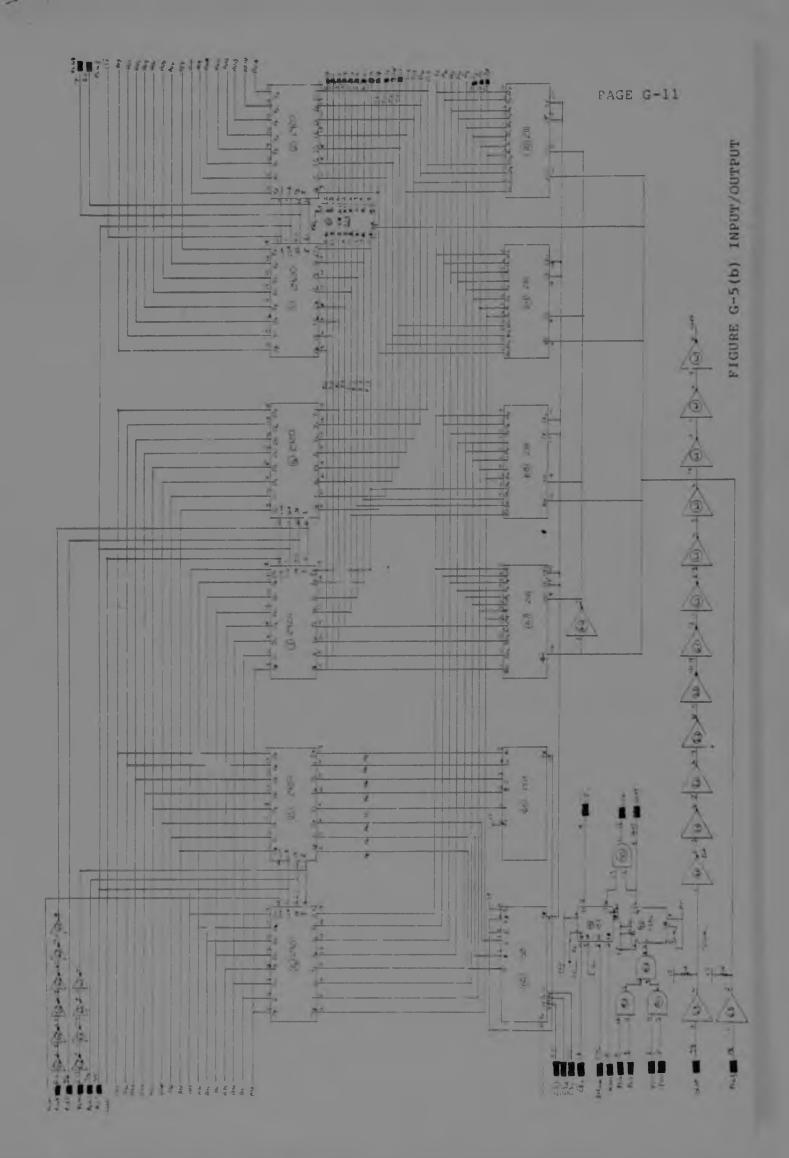

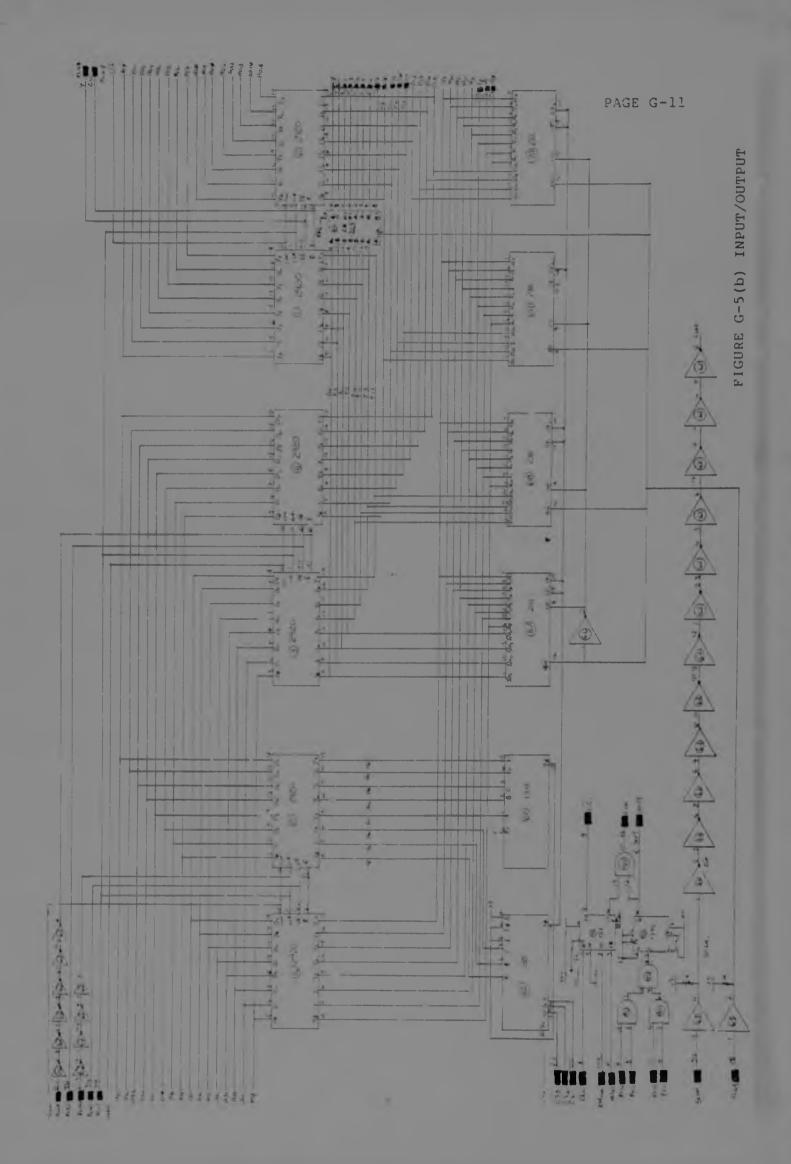

| G-5(b) | Input/Output                         | G-11 |

| G-6(a) | Computer Control Unit                | G-13 |

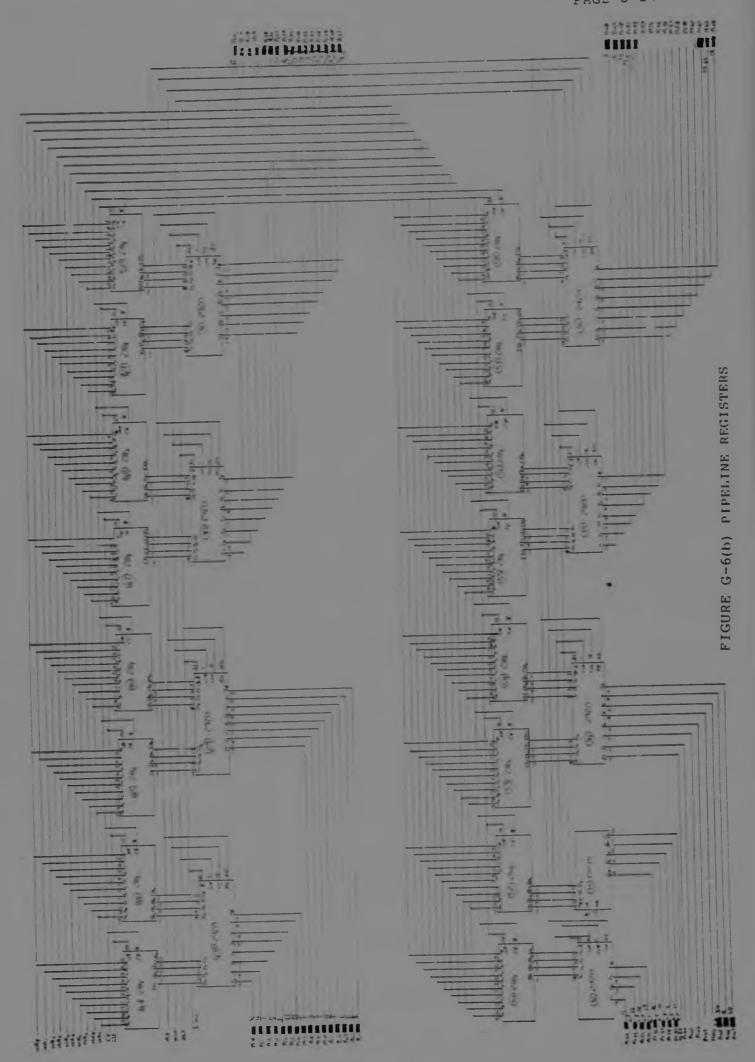

| G-6(b) | Pipeline Registers                   | G-14 |

| Graph: |                                         |      |

|--------|-----------------------------------------|------|

| No.    | <u>Title</u>                            | PAGE |

|        |                                         |      |

| 1      | Failure Rate of Components              | 1-8  |

| 2      | Average task delay time as a            |      |

|        | function of task Characteristics        | 1-21 |

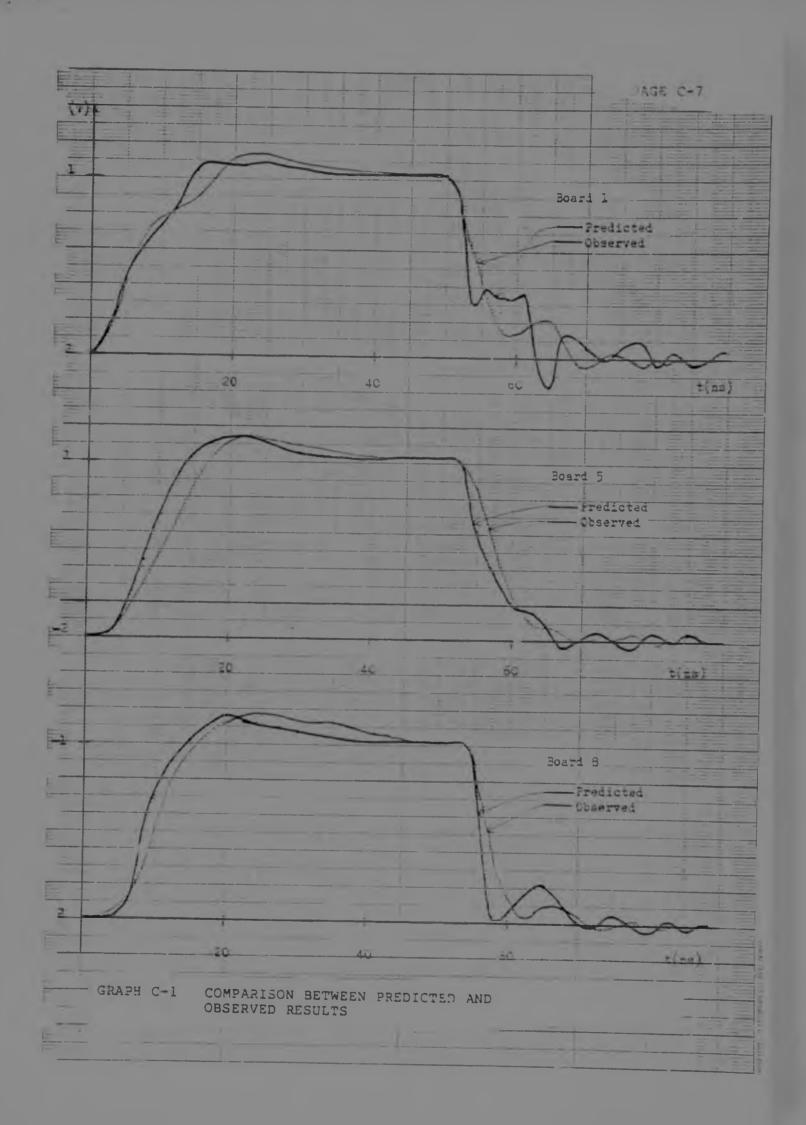

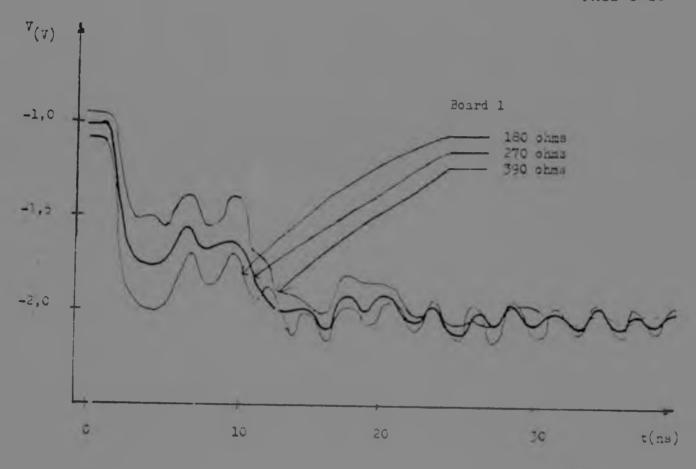

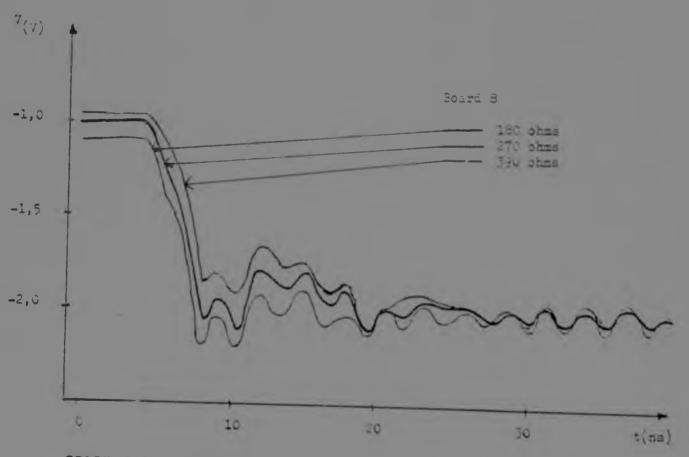

| C-1    | Comparison between predicted and        |      |

|        | observed results                        | C-7  |

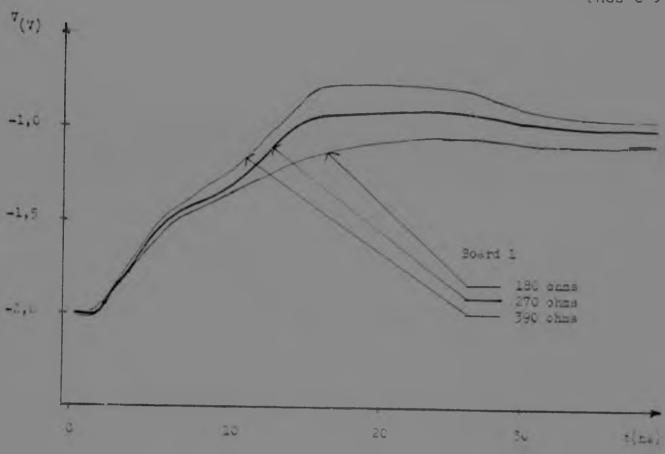

| C-2    | Comparison of rising edges for          |      |

|        | various termination resistors.          | C-9  |

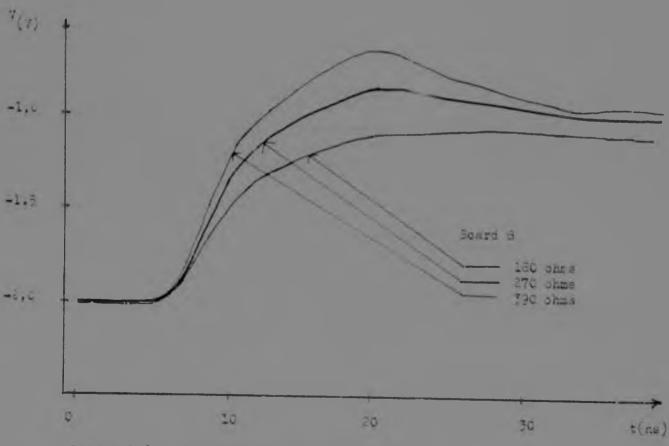

| C-3    | Comparison of falling edges for         |      |

|        | various termination resistors.          | C-10 |

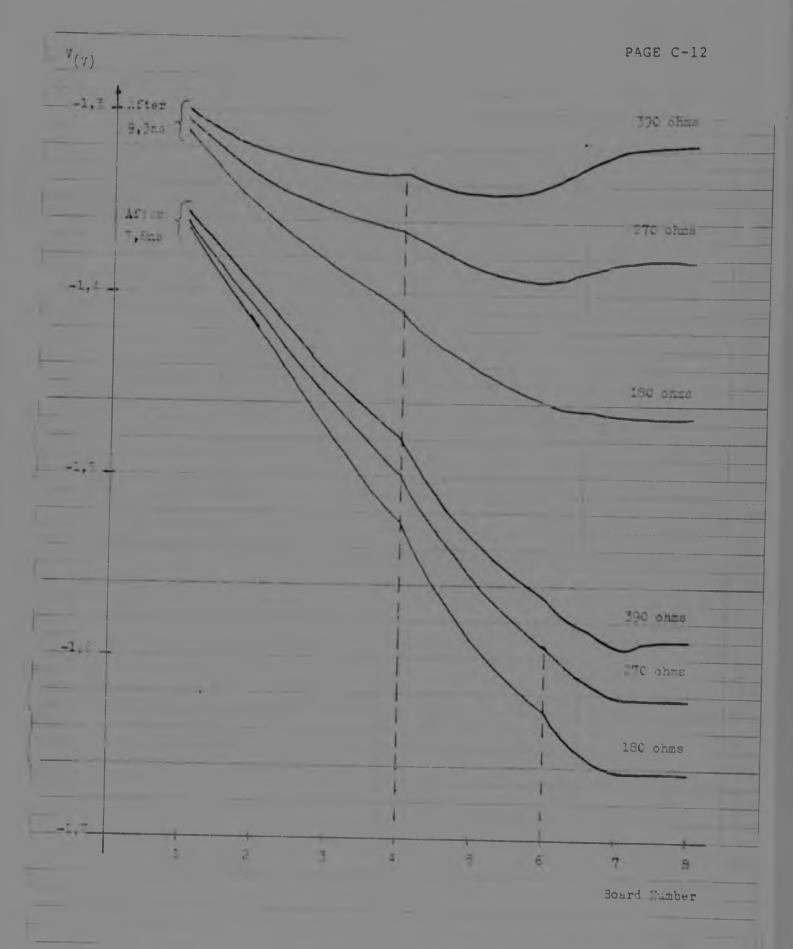

| C-4    | Comparison of the Voltage cross-section |      |

|        | on the bus at various times for         |      |

|        | various termination resistors.          | C-12 |

| Tables |                                         |      |

| No.    | <u>Title</u>                            |      |

| 1.1    | Cost/Performance ratio                  | 1-4  |

| 1.2    | Reliability of Components               | 1-6  |

| 7.1    | Execution Times                         | 7-11 |

#### CHAPTER 1

#### INTRODUCTION

"An I directed my heart to know wisdom, and to know madness and folly ,but I have perceived that this also is a torture of the spirit. For where there is much wisdom there is much vexation, and he that increaseth knowledge increaseth pain" [Eccelesiastes i 17,18].

This thesis proposes a technique for interconnecting a large number of microprocessors to form a simple, inexpensive but efficient computer system. The system inherently modular thus enhancing reliability, mai mainability, and testability.

#### 1.1 Tre Growing Demand for Computing Power

In order to cope with the rapid advance of technology and the ever-increasing demands of society, particularly in respect of automation, there is a need for the provision of more computing power at lower cost. One need only to look at fields such as those mentioned below to see that the 'supercomputer' is very much in demand.

Short-range weather fore attemption of computer assisted highly complex weather modell in Computer assisted tomography (Figure which involves high-speed signal processing and imaging, as all as the rod lling of organ such as the heart, nails advanced equipment for computing at speeds approaching 100 million floating point operations (megaflops) per second [SLA]. Nich in fu ion researchers could use a computer 100 times faster than any existing machine for modelling the plasma instabilities of proposed fusion power generators [SUS 80].

One of the world's most complex undertakings in the past two decades has been the USA Department of Defense (DOD) Ballistic Ni sile Program. A critial part of the large research and development invist at in this program has been the effort to develope differencesing hardware and software technologies to meet the computational challenges of this complex problem. The Ballistic Missile Program needs a computing system that will deliver a throughput of hundreds of megaflops per second, with a high degree of confidence that correct execution will occur. This challenges even the most advance to hipologists. [DAV 86]

The computer engineer, who takes on himself the burden of designing such a machine faces a great challenge. He must bear in mind that a computer is ultimately designed for the end user, and it is the user's evaluation that counts, as it is he who will be in the most intimate relationship with the computer. The computer, therefore, has to be user acceptable in terms of reliability, maintainability and safety.

#### 1.2 Distributed Control

Amongst the many criteria which determine the choice of a particular design, is that of overall cost. A feel for this criteria may be established in table 1.1. In this Sugarman compares the processor cost/performance for a particular sample problem requiring 83000 flops for each iteration. It can be seen that the AP-120B peripheral array processor is 7 times as cost-effective as its nearest rival the CRAY-1 supercomputer [SUG 80].

| Machine     | MElops      | \$/flop | installation cost in \$M |

|-------------|-------------|---------|--------------------------|

| AP-120B     | 5.9         | .03     | .15                      |

| CRAY-1      | 38.4        | .21     | 8                        |

| STAR-100    | 16.8        | .48     | 8                        |

| VAX 11/780  | . 26        | .77     | .2                       |

| CDC 7699    | <b>3.</b> 3 | .91     | 3                        |

| ILLIAC IV   | 9.1         | 1.1     | 10                       |

| CDC 6600    | .63         | 1.59    | 1                        |

| IBM 370/165 | .87         | 2.3     | 2                        |

TABL: 1. 1 COST/PI DRMANCE RY ' [SUG 80]

(A MegaFlop(Mflco) is a million floating point operations.)

Of interest from the above comparisions, is the observation which may be made that parallel processors, which are cheaper than supercomputers, can be used in situations such as those mentioned previously.

#### 1.2.1 Reliability

An essential trade-off to be considered in computer design is the complexity of the computer versus the power (or throughput). It is common knowledge that the more powerful a computer is, the more complex it becomes [SUG 81]. It is also common knowledge that complex electronics, unless highly integrated, becomes increasingly unreliable and costly. This is easy to explain:— From table 1.2 it can be seen (a) that the reliability of a computer board decreases 40-fold when compared to the reliability of a single integrated circuit because of the increase in components and complexity, and (b) that the reliability decreases dramatically as the number of components per system increases.

| Component                    | Order o | f Magni | tude of Fi | its |

|------------------------------|---------|---------|------------|-----|

| Transistor                   | 10      | to      | 100        |     |

| LSI component                | 103     | to      | 1000       |     |

| Solder connection            | 2       | to      | 20         |     |

| Switch (percontact)          | 30      | to      | 300        |     |

| Plug connection (per contact | :) 3Ø   | to      | 300        |     |

| 1 Board computer (25 chips)  | 4000    | to      | 40000      |     |

Table 1. 2 Reliability of Components [KOP 81]

(1 FIT = Farlure in 10\*\*9 hours i. e. 115000 years)

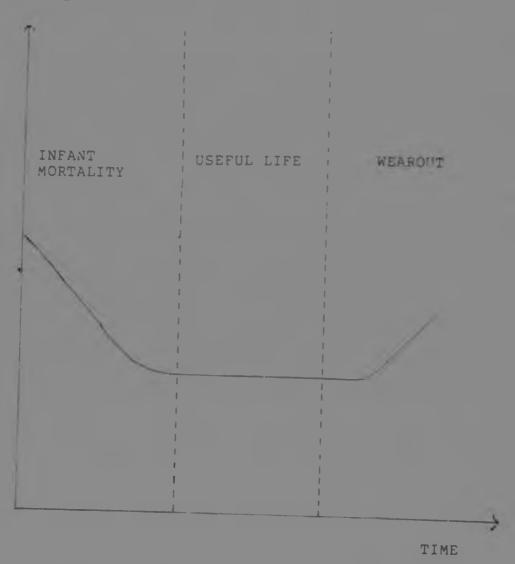

Graph 1 shows the characteristic curve for an electronic device. Early failures, such as infant mortality or burn in failures, occur at a high initial rate which decreases when the weak units have died out. The useful life period, which is the most important period because it is the key to reliability prediction, is followed by the wearout period. Wearout failure results from degradation of the strength of a device and exposure to the environment [DOY].

FAILURE RATE

GRAPH 1 FAILURE RATE OF COMPONENTS

The society in which we live is becoming very safety-conscious, and increasingly dependent on computers. Therefore a computer which has the function of, say, controlling production machines or on which we rely for the handling of critical data, has to be extremely reliable. One need only look at what happened at Three Mile Island. The nuclear reactor at Three Mile Island was controlled by lardwired logic and many small computers. There was no central controlling facility nor was there communication between the distributed control points. At the moment of crisis the operators were faced with many indicator lights and perhaps, if there had been an interconnection of the control points, the near-disaster might not have occured. For this to be available, clearly a highly reliable computing system is vital. NASA, too, has an aircraft energy efficency research program needing ultra-reliable computers that would counteract faults automatically. The aircraft flies very close to the limits of stability and therefore a computer with a fast response time is needed (rather than a human) to control it. The probability of a computer failure during a flight must be less than the probability of mechanical structure failure during the same period. Thus an ultra-reliable and fast computer is needed.

Reliability is normally defined as the "probability that a system will function within the specified limits for at least a specified time under specific environmental conditions" [KOP 81]. It is concerned with all the parts of the system (hardware, software, printed circuit boards, etc.), their interaction, the intercondition interaction, the intercondition interaction on the mechanical construction.

In striving to achieve a high degree of software reliability, problems such as software validation are encountered. Present techniques are inadequate for evaluating the reliability of software, and perhaps the only way of checking software is by exhaustive testing [LAM]. Bernhard maintains that system validation problems are primarily related to software, and that no guidelines exist for determining software reliability [BERD]. Making the software simple and well defined can help in solving these problems, but the programmer can never claim with total certainty that his program is error-free (see 1.4).

The reliability of a computer system requires a thorough investigation. Reliability involves both software and hardware and it was decided to limit the study of reliability in this thesis primarily to that of hardware (appendix J). Software reliability is dealt with on the "keep it simple and well-defined" precept.

One of the most critical factors influencing the reliability of a computer system is the interconnection structure of the system. This is because, although the reliability of the individual components can be maximized, the overall reliability of the system will be related to the component interconnections, which are not usually duplicated and are inherently unreliable (being mainly mechanical in nature).

In practice, there are various techniques available for attaining a high degree of reliability. These essentially achieve reliability through either the use of inherently highly-reliable components or through the introduction of redundancy. (Redundancy here implies that the system contains more resources than are absolutely necessary for normal operation). According to Toong [TOO] highly-reliable systems are "systems with a structure independent of any critical resource that has a relatively high failure rate."

The cost of increasing the reliability of components achieved during aroust tro, is very high. Therefore rault-tolerance is normally adopted on the premise that it is more economical to build redun ant systems than to strive the extreme component formally. A rault-tolerance component system is one which can survive multiple faults that would normally bring a conventional co-puter to a halt [STI].

Of importance in a redundant system is the ability to detect an error. Error detection presupposes that the result of a step in a promount of a can be related to an acceptance criterion. In a system with redundancy, additional resources typically are used to form an error detection module which may be separated from the actual active processing addules [KOP 81].

A key issue in fault-tolerance design is the size of the unit that is to be replaced in the event of a failure - often termed the amallon Replaceable Unit (SBU). The SRU is generally visualised as the unit which is removed by the service enginer once he has localised a fault to a particular unit, which is then replaced by a identical one. It is also clear that an SRU must be testable - specifically this requires it to have well defined interfaces[KOP 81]. The SRU could be a resistor or transistor at one extreme or a complete board at the other. Since the costs of electronic components are steadily decreasing it becomes economically

feasible to think in terms of a complete board as the SRU.

From the above it may be concluded that a well-structured computer should therefore have inherent fault-tolerance built into its architecture, by having redundant components. By adop . uch a design, however, it would seem that reliability is achieved at the expense of simplicity. This thesis discusses an architecture for a computer system that is reliable, partially fault-tolerant and (of importance) simple and well-structured.

#### 1.2.2 Maintainability

The user of a system is primarily concerned with the availability of the system for his use. Availability is a function of the Mean Time Between Failure (MTBF) and the Mean Time To Repair (MTTR). As a failure occurs, the faulty module is replaced by the service engineer and the user can then carry or operating the machine as if nothing had happened. Provided the principle of fault-tolerance is adopted, however, during the diagnosis and repair time the user will simply experience a slight drop in performance.

There is clearly a trade off between maintainability and reliability - both being linked to the availability of the system (see appendix J). Maintainability, which can be defined as the probability of repair in a given time, implies that the system must be modular. If the SRU is extracted for repair, the system must be able to tolerate this removal and recover once the module is re-inserted.

A module is characterised by the function it performs. It is essentially a 'plack box' which transforms a set of inputs to a set of outputs. In designing systems using modules the designer assumes that other modules, except the one on which he is working, work to specification. Testing is done in a similar easy fashion.

Of importance too, is the practical realisation that once a computer system has been installed, the user inevitably needs to increase its capacity! Enhancement of a computer system can be achieved much more readily in a well-structured, modular design.

### 1.3 The Influence of Technology on Architecture

The advance of technology is sometimes too rapid for the system designer, in that by the time his design is functional there may be newer and more powerful components available which might more easily accomplish his required tasks. This problem is never more apparent than in the world of electronics, and particularly, the digital area where the pace of technological innovation is staggering.

The Electronic designer has three approaches available to him when utilizing state-of-the-art digital hardware. These may be summarized as follows:-

- 1. The use of Custom Designed Integrated Circuits.

The engineer designs highly complicated integrated circuits from the transistor junction level—

normally using the support of a Computer Aided Design system (CAD). These components are then fabricated especially to meet the required function. Clearly cost is a problem unless volume is high (typically > 10000 units).

- 2. The use of Readily available VLSI. The engineer attempts to utilise integrated circuits which have already been manufactured and which perform specific functions.

3. The use of Semi-Custom Logic (e.g. a Logic Array). this technique the integrated circuit manufacturer produces a chip which is complete from the semiconductor point-of-view, but which lacks the final interconnection of the various logic functions that are performed by the semiconductor junctions. Thus the designer of a circuit typically has two to three thousand logic gates available for his design. Using CAD techniques, he then creates a system using only the types of components available on the particular array chip in which he is interested. Once again, using CAD facilities, the designer optimises Interconnection of the gates to give himself a system which meets his requirements. The final interconnection of the components (the metalisation process ) is relatively cheap, and the approach is is cost-effective for a medium level of production [ROD 82].

In addition to the points mentioned above, a fundamental premise in design is that a designer should strive to utilise state-of-the-art technology; this, of course is in itself a situation requiring much thought. A case in point is the Josephson Junction. Conference papers continue to be delivered on this technology but the scientific world still waits for a commercial computer based on Josephson Junctions.

Josephson devices, which are based on superconductivity and tunnelling, are very attractive for ultra-high-performance computers. They are extremely fast-switching (<10 pico seconds) have extremely low power dissipation (< 500 nano watts per circuit). However, they have to operate at near the Absolute Zero temperature (-270 deg C), so that they can function according to the specifications. This temperature requirement causes undue environmental complexity as well as additional costs for refrigeration, and inconvenience of system debugging and servicing [ANA 80].

Therefore even though Josephson Junctions are undoubtedly superior in most aspects to any other logic family available, there is a natural reluctance amongst computer designers not to use this technology until it has been proven and tested.

An important factor which has to be considered is the local situation. As the work for this thesis took place in relative isolation from the centres where electronic technological advances are normally made, the decision was made to design a completely modular system based on locally available technology. This ruled out the use of Custom designed circuits, as well as that of logic arrays - this latter industry being still in its infancy in South

Africa[NOV]. However the majority of leading Integrated Circuit Producers are represented in the country, and thus the bulk of commercially available components could be considered.

Finally from a maintenance point-of-view the approach adopted appears to have much merit. One has always to ensure that the local maintenance personnel can cope with the technology they are servicing; also that replacement components are readily available.

#### 1.4 Software

The complicated aspect of software reliability has not been dealt with in detail, as it is beyond the immediate scope of this particular investigation.

However, a few general guidelines which should be adhered to in attempting to produce reliable software have formed the basis of all software developed in this project. These are as follows:-

1. The specification of the program should be kept simple and accurate and must be well documented to allow non technical persons to understand the software

- 2. The software must be well designed with clear meaningful documentation, in order to reduce effort in testing and maintenance.

- 3. The software must preferably be organised in a tree structure, in order to make reading and understanding easier.

- 4. The software should be written in a modular structure with loose coupling between modules, so that any module can be extended, replaced or removed without affecting the other modules.

- 5. The software should be designed in a top-down fashion, which first describes the problem in a very high-level way, and then proceeds to give lower levels of description until the level is reached which contains definitions of indivisable functions | LAM |.

Because most of the operating system has been implemented in hardware, and only a minimal amount of software (designed using the above principles) is required to complement the operating system, it is felt that this approach ensures a relatively high degree of software reliability. However it must be emphasised again that this aspect of reliability was not considered in detail in this thesis.

## 1.5 Multiprocessors

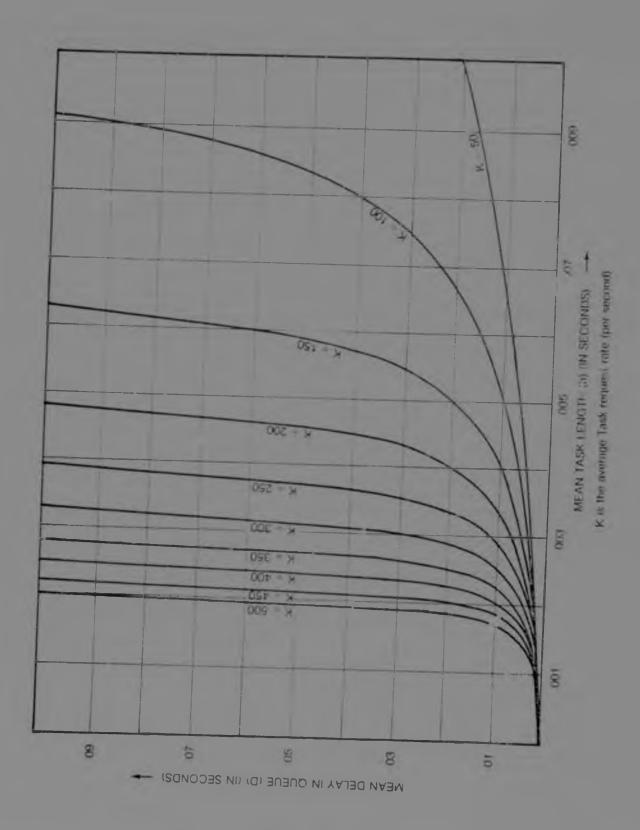

Kould has applied the theory of traffic movement through a telephone exchange to the analysis of the performance of multitasking industrial control computers and has produced a graph (Graph 2) which mirrors the expression derived for the mean delay experienced by a task in a gueue which can form in a multitasking computer system [ROD 75]. This was done in order to predict the performance of the system. As can be seen, the delay time in the gueue increases as the average reguest rate increases. There are clearly various ways to increase throughput of a system as may be deduced from these curves:

GRAPH 2 AVERAGE TASK DELAY TIME AS A FUNCTION OF TASK CHARACTERISTICS [ROD]

- 1. Make the task length shorter, i.e. simplify tasks or increase speed of processing

- Decrease the average request rate, i.e. reduce the demands made on the processor

- 3. Make the computer faster, i.e. increase overall operating speed (as well as achieving (a) above).

- 4. Increase the number of processors, i.e to decentralize the processing.

Powerful, large-word-size mainframe computers and supercomputers have made high-data rate processing feasible, out these systems are not economical for laboratory environments, data acquisition, process plants or reduction applications. Minicomputers on the other hand are economical, but are technically unsatisfactory because of their limited computing speed and smaller fixed-point format. [ALE 81]. Therefore the microprocessor, which is cheap, and which can be interconnected to form a powerful multiprocessor computer, can fill the gap left by the two other computer systems.

Decentralisation of a computer system implies that there is a distribution of intelligence (i.e. processors). As has been seen in section 1.1, parallel processors (of which the multiprocessor is one type) compare very well with 'supercomputers' on a cost/performance ratio. There is less reliance on a centralised facility, and processors can be added on a more flexible basic and in smaller increments.

Multiprocessors inherently rely heavily on parallelism to enhance throughput and computation. With such a hardware structure many elementary data routing and processing functions can be implemented concurrently, improving total processing speeds by 10 to 100 times over typical minicomputers.

A multiprocessor architecture increases productivity through parallel processing, and maximises the likelihood that a processor will be available when it is requested. The system can generally be tailored to user requirements in a more flexible manner than can a centralised facility, because each processor in the system can be used to perform a separate function.

A multiprocessor computer should also be inherently modular and therefore the cost of increasing its processing capability is smaller than that incurred when expanding a large computer. Redundancy at a hardware level is naturally easier in a multicomputer than in a monolithic central facility as extra modules (which are added on to take an active or passive part in the system) can take over the execution of a task in the event of a processor failure.

As has been pointed out in appendix J, a multiprocessor system that has redundant units is ideally more reliable than a uniprocessor system. An additional factor to consider when designing a redundant modular system is that the system should 'gracefully degrade'. This idea is illustrated in the following example. An on-line airline booking system is a distributed computer with user terminals in each booking office and with a centralised data base. The failure of any terminal should not inhibit other users from accessing the common data base. This is usually referred to as "graceful degradation" in that failures will accumulatively affect the overall system performance but not cause immediate and total system failure.

In such a system reconfiguration is, however, necessary when a permanent error, like a processor failure, occurs. At the conception of a redundant system it has therefore to be decided at what level redundancy is to be implemented — at system level, subsystem level or at a component level (as in the to discussion of SRU above). Therefore it is logical to make the SRU (i.e. a complete board) the redundant component as well.

From the previous sections it may be seen that the choice of components of a multiprocessor is critical. As mentioned in 1.2.1 the SRU should be a complete circuit board. A microprocessor computer board will provide a convenient basis for reconfiguration after an error and should therefore be the SRU.

It can therefore be concluded that a multiprocessor computer is a simpler alternative to a bigger computer in most applications.

### 1.6 Ramrod: A Multiprocessor Architecture

Ramrod, as the multiprocessor structure developed in this thesis has been named, was designed using a master-slave approach as it was felt that there was a need to provide for supervision of the slave processors with respect to their intercommunication, execution of tasks and probable failure. This is of particular importance in an experimental system which Ramrod essentially is.

For this reason it was concluded that the master had to be more sophisticated and more powerful than the actual processors. Therefore the master was designed using bit-slice technology and the instruction set was custom built to suit the application (see 4.2), whilst the slave processors were selected to be simple, single-board computers. Using bit-slice technology for the master implies that the designer has complete control over the architecture and many features are therefore included to provide this with properties inherent in operating systems.

### 1.7 Conclusion

Many inexpensive and relatively powerful single-board computers are currently available on the market and can therefore form the SRU of the multiprocessor system. In the event of a processor failure, the faulty processor board can be replaced by a working one, and redundancy achieved at the same level. The multiprocessor system can have redundant idle CPU boards ready to take over should a processor failure occur.

This approach to architecture is currently receiving much attention: a leading German Computer Architect Wolfgang Giloi maintains that "The distributed multiprocessor system is the only known architectural form that can satisfy high cost effectiveness, modular extensibility, fault tolerance and simplification of software production and maintenance simultaneously" [GIL BEHR].

Any multitasking computer system has its activities co-ordinated via an operating system. In the case of a multiprocessor the operating system may itself be distributed with a part of its functions performed by the master processor and other parts by the various slave processors. This should result in a highly efficient computer system as there is only partial reliance on the master processor, and each processor shares in the execution

of the operating system [TRAKH]. Of interest is the implication that the various component parts of the operating system can themselves be executed truly in parallel!

As will be shown in the next chapter, the preferred interconnection strategy for a multiprocessor is a shared bus in which the processors access common memory. As will be shown this is an optimal solution despite claims that a shared bus has serious bandwidth limitations.

Ramrod has such a shared-bus structure with a wide bandwidth, this having been achieved by a technique that appears to be novel. Ramrod has been designed, built and tested. The prototype, although suffering from certain timing problems, has been successfully evaluated and the methods used are shown to be viable. The result is a multiprocessor system which makes use of commercial well-understood computing elements and which is reliable, modular and easy to maintain.

### CHAPTER 2

# MULTIPROCESSORS AND AN INTRODUCTION TO RAMROD

"Two are better than one because they will have a good reward for their toil. For if they fail the one will lift up h.s fellow, but woe to the single one that falleth for he hath no companion to lift him up " [Eccl iv 9,10]

Before dealing with the actual scheme adopted in Ramrod this chapter will provide a general background to multiprocessors and the various possible strategies which may be used. The interconnection philosophy of Ramrod will then be discussed in this light.

# 2.1 Mul processor Structures

A multiprocessor typically has the following attributes:

- 1. The system contains two or more processors of comparable capabilities.

- 2. All processors share access to common memory, but may have local memory.

- 3. All processors share access to Input/Output channels, control units and peripheral devices.

4. The entire system is ideally controlled by a simple operating system. [ENS 74]

Innerent in this definition is the concept of a multiprocessor system as a so-called 'tightly coupled' distributed computer. This implies that the various processors in the system are in close proximity to each other and have access to a common memory and common Input/Output system.

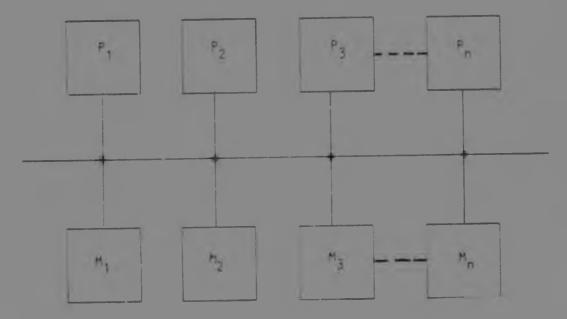

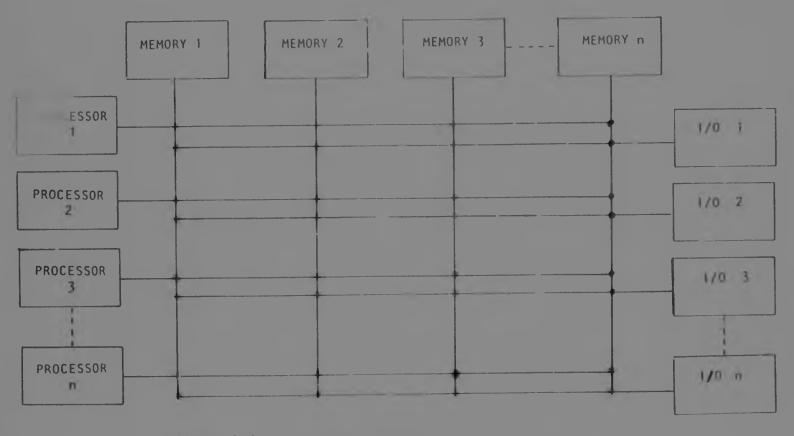

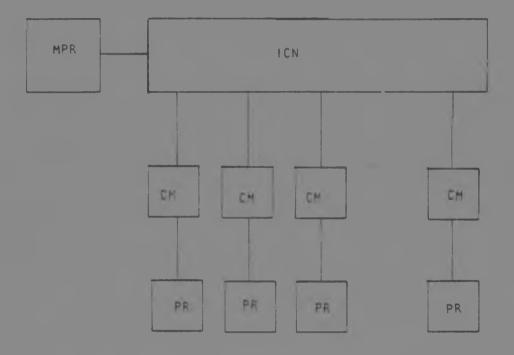

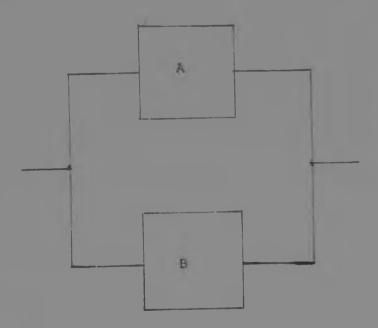

A typical multiprocessor will take the form shown in Figure 2.1. Processors (P1-Pn) are connected to Memory Elements (M1-Mn) or other peripheral devices. Thus communication between the processors and resources (mem, I/O, peripherals) is an escential communication of ten referred to as the Processor/Memory switch.

FIGURE 2.1 TYPICAL MULTIPROCESSOR

The following sections provide more detailed descriptions of the major interconnection technologies and their advantages and disadvantages. The shared bus, the cross bar switch and the multiport memory are compared in terms of cost, reliability, system throughput and transfer capacity. Discussions of systems using these architectures are to be found in appenndix D.

### 2.2 Interconnection Strategies

# 2.2.1 Shared Bus

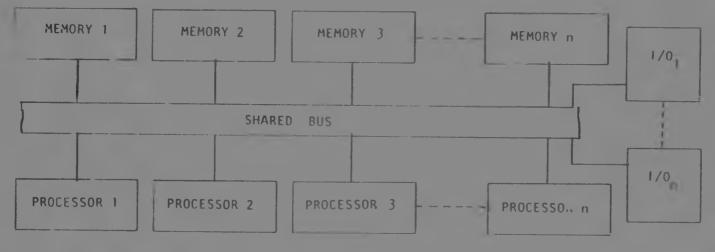

The simplest switch for a multiprocessor system is a common bus connecting the units as shown in Figure 2.2.

FIGURE 2.2 SHARED RUS

The shared bus can be centrally polled, i.e. the processors only transmit when selected by the controller. Bus contention is avoided by using schemes such as:

- Fixed priorities, which allow processors with a higher priority to gain access to the bus if another lower priority processor presently has access.

- 2. First-in-first-out: the processor which first made the request is granted access to the bus

- 3. Daisy chaining: The processors are asked in turn whether they have made a request, and only then can a processor be given access to the bus.

On the other hand, the bus may be interrupt driven by the processors, which request bus usage. This scheme allows random usage of the bus. However an interrupt system can cause problems, if, during one processor's control of the bus, a second processor requests the bus, access can be granted to this second processor, and the first's data is lost. On the other hand, should all interrupts be disabled during a bus access then the requesting processors will have to wait for access and processor idle time is increased.

The bus can be a Time-Division Multiplexed (TDM) bus, where each processor is allocated a time slot, or it can be Frequency-Division Multiplexed (FDM), in which each processor has a particular transmit/receive frequency.

The shared bus is simple to design and construct, but has bandwidth limitations inasmuch as the number of active or passive units connected to it is limited [WEl 81]. This reduction in bandwidth results because when more units are connected to the bus, the bus is simply unable to keep up with the increase in communication which accompanies the addition of units [ZOC]. As there is only one path for all data transfers, the total transfer rate within the system is limited by the speed of access of devices onto the bus and the actual bus bandwidth.

The shared bus is usually connected to a common memory (indeed so are the other strategies) and therefore memory contention is also an obvious problem in that there is only one bus and one access to the memory connected on the other side, so there is a likelihood that two or more processors will try to access the same area of memory simultaneously. This problem can, however, be overcome by dividing the memory into segments, and allowing only one processor at a time to access a segment.

This scheme is the least costly in terms of the hardware used, and is also the least complex in terms of components as the bus can be totally passive. Modification is achieved simply by physically dding or removing functional units. However, a single bus system is naturally unreliable in that if the bus fails then a total system failure occurs.

### 2.2.2 Cross Bar Switch

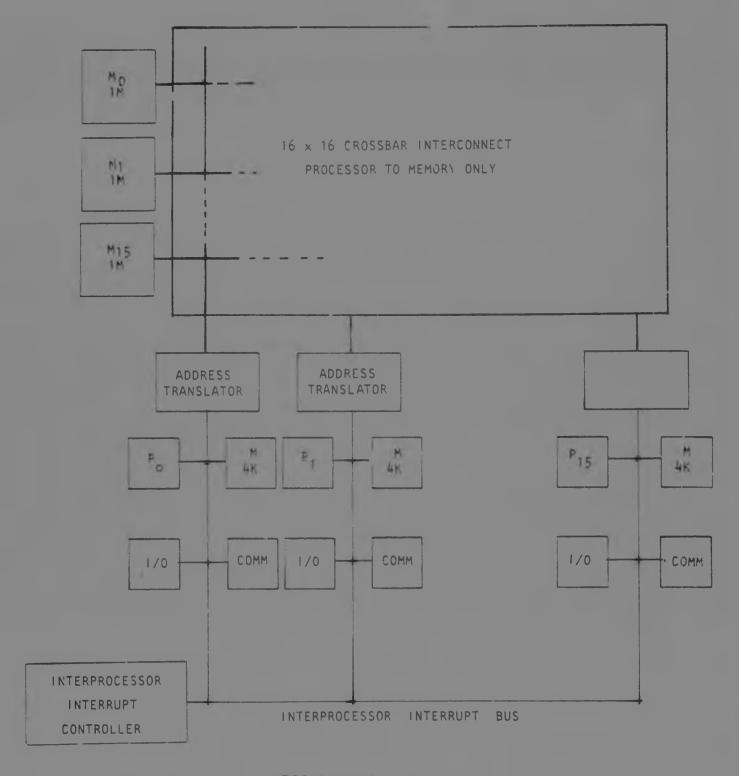

The cross bar switch as shown in figure 2.3 has separate paths from the processors to each memory and I/O unit. The functional units (processors, memories and I/O) need not be concerned with the bus interface as the switch contains all the necessary logic.

FIGURE 2.3 CROSSBAR SWITCH

This is the most complex interconnection scheme because the number of connections is necessarily large and because of the extra logic needed in the switch. The complexity grows exponentially as the number of units becomes large. Functional units, however, are simple and inexpensive because they do not need the extra logic to drive the interface and the potential exists for a high data transfer rate, since there is a separate path available to each unit.

Reliability is reasonable and can be improved by redundancy of the units. System efficiency is high because simultaneous transfers between processors and memory units can be accomplished.

Clearly the switching elements are the major drawback to such a scheme, but it must be pointed out that Intel is about to produce an LSI circuit with a large number of cross-bar switches for their new range of multi-processors [ENS 74LThis will obviously reduce the cost factor as well as the complexity discussed above.

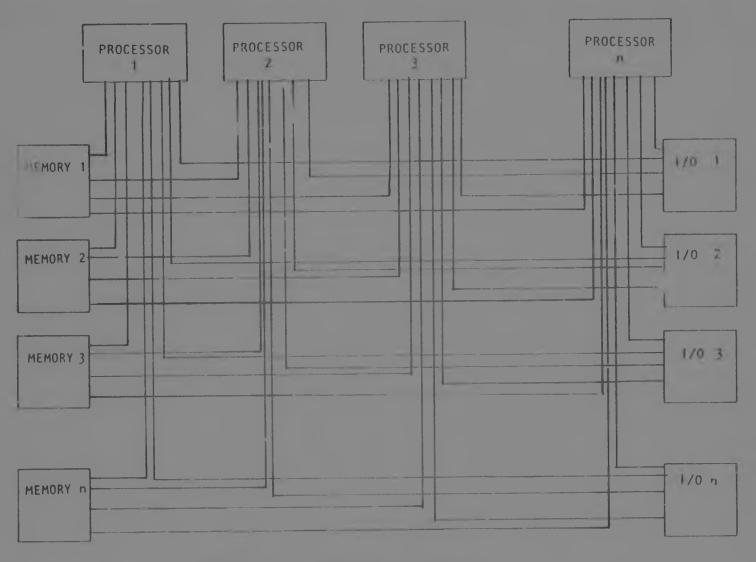

# 2.2.3 Multiport Memory

In a multiport memory system the control, switching and priority arbitration are concentrated at the interface to the passive units, and not in the switch as in the cross bar scheme. Figure 2.4 shows that each processor has a separate port and bus connecting it to each memory and I/O unit.

FIGURE 2.4 MULTIPORT MEMORY

This approach is the most expensive, since multiport memories are costly and each memory has to have contention logic built in, in order to arbitrate between processors competing for the resource. High data transfer rates can be achieved, but expandability is difficult as more logic is required to increase the number of memory ports, or to share the existing ports amongst all the processors.

This system has its use in a system which has a limited number of processors, but clearly becomes unwieldy as soon as the number gets large.

#### 2.3 Shared Memory

All of the interconnection strategies, previously mentioned, usually use shared memory which provides for a means of interaction between microprocessors. This interaction can be enhanced if there is no distinction between local memory of a single processor and global memory of the multiprocessor system. This is clearly a unique feature which has the advantage of teing able to incorporate a truly distributed data base, since processors can address all the memory simultaneously. However care must be taken to ensure security of data.

### 2.4 Time-Division Multiplexed Bus

The Time Division Multiplexed(TDN) shared bus offers the best capability of all the interconnections discussed as it is simple, cheap, easy to implement and is a passive interconnection. The apparent limitations of the TDM bus are:

- 1. Memory Contention

- 2. Reduced Bandwidth

- 3. Bus Contention

Fortunately these can largely be overcome as outlined below.

### 2.4.1 Memory Contention

A shared bus, as mentioned previously, is usually associated with common memory and therefore memory contention can occur. A system that allows the programmer to use a range of program addresses which may be different from the range of physical memories available (known as virtual memory addressing) may circumvent memory contention.

# 2.4.2 Bandwidth Limitations

Bandwidth limitations can be overcome by using high-speed technology to achieve a high data communication rate on the shared bus. In addition if the speed of access to the bus is increased then the overall bandwidth should also be increased.

### 2.4.3 Bus Contention

Examining the simple time-shared bus, it is found that contention occurs when several processors are making heavy use of the bus and when there are no mechanisms to resolve this contention (and cause processor idle time). Therefore a model of the shared has can be made as a master/slave relationship (where each slave runs a single user task and the masters provide the requested service) in order to consider the problem of contention.

Let the slave request rate = 1/L in secs and slaves only process when serviced by a master.

Let

N = number of slaves

$N_{avg}$  = average number of slaves

M = number of masters

$M_{avq}$  = average number of masters

P = L/U, and Pi = probability of i slaves in queue.

$N_{avg}$  = average number of total busy processors

Wavg = average waiting time in gueue.

$S_{m} = 1/U$  expected service time of requests

$W_{m}$  = expected waiting time in queue

It can be shown [TOO 78] that

$$N_{avg} = M(1 - \sum_{i=0}^{M-i} M_{i}) P_{i} = M_{avg}$$

$$W_{avg} = W_m + S_m = \frac{N - N_{avg}}{N_{avg} \cdot L}$$

This simply states that the average slave waiting time increases as more slaves become idle  $\{N-N_{avg}\}$  while waiting for service from masters.

The same conclusion can be reached by examining the bus utilization factor, which is the fraction of the time that a particular processor will make use of the data bus during an instruction cycle.

This master/slave approach reinforces the need for some sort of control to supervise the allocation of memory to processors and the allocation of time slots to processors for execution of tasks. If this time slot (or bus utilization factor) is reduced then a significant increase in system throughput is achieved.

# 2.5 Supervisor Control

The key to the success of a master/slave multiprocessor system from the type of manner point wathously selected. Software has been shown to be less reliable than hardware [KOP 81] and a large program can never really be proved correct. Rodd [ROD 76] has shown in his investigation that the implementation of an operating system kernel in hardware has much promise. The use of bit-slice technology offers the designer a chance to design the architecture of the master provides to master controller was designed to contain several features of the kernel of an operating system. This will be discussed at a later stage.

### 2.6 An Overview of Rarrod

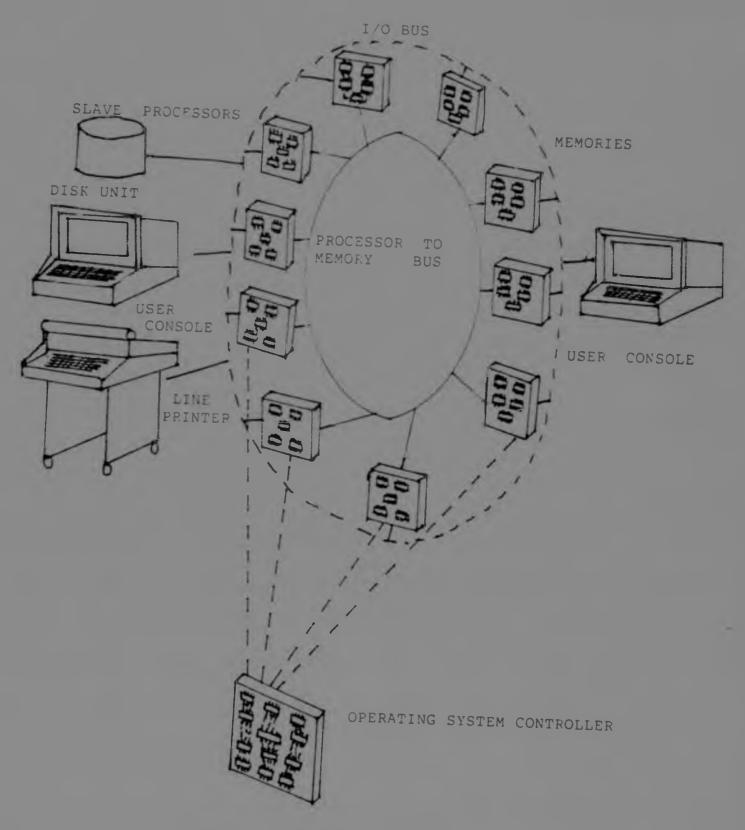

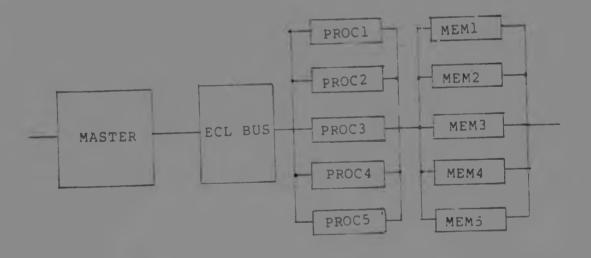

named on the information proviously discussed, Ramrol whose simplified diagram is shown in figure 2.5, was designed with the following features:

- 1. Distributed Operating System

- 2. TDM shared bus

- 3. Master-slave processors

- 4. Tightly-coupled slave processors

- 5. Common Shared memory, with no distinction between global and local memory.

- 6. Intelligent Input/Output Control

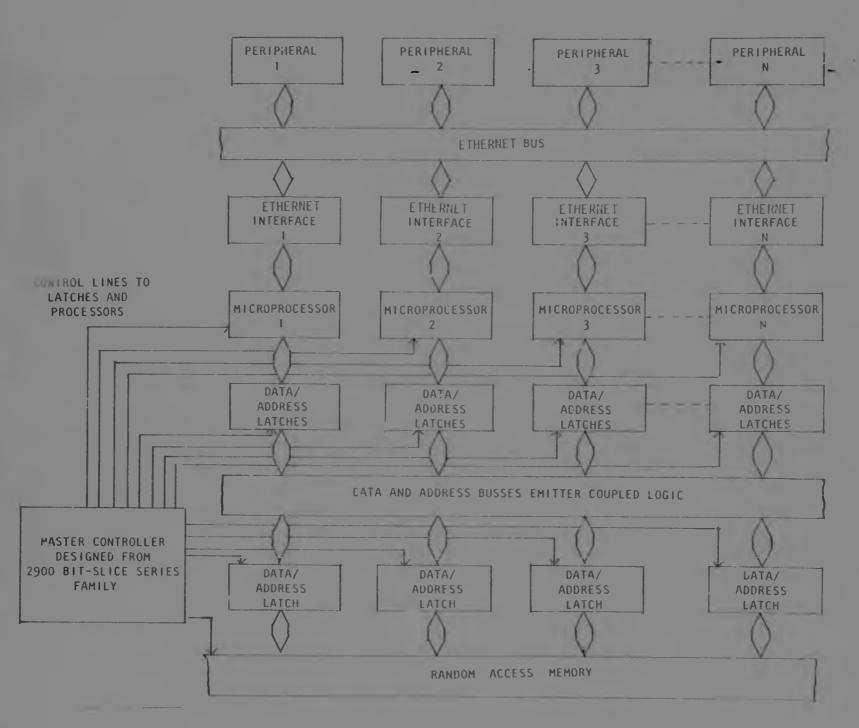

FIGURE 2.5 SYSTEM DIAGRAM

### 2.7 Conclusion

The multicomputer system with distributed control is probably the only architectural form that has the potential to satisfy all major architectural goals such as cost effectiveness. Moreover, and decomposition of software complexibility [GIL BEHR]. The multiprocessor is an interconnection of uniprocessors and it is this interconnection scheme which forms the basis of this thesis.

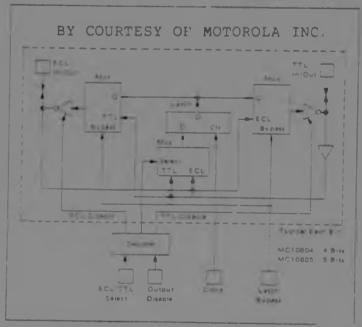

by a bit-slice processor which has the function of a system supervisor. There are presently 5 slave processors each of which are defined from the first microscopic. The memory modules, which initially consist of 256 byte segments, are interfaced to the processors via a time-shared common but, which initially military counted Louic (ECL).

The I/O section has not been implemented in the prototype but it in support of a parallel development (appendix H). The following chapter describes the hardware structure whereas chapter 4 discusses the software in more detail.

#### CHAPTER 3

### A REAL-TIME OPERATING SYSTEM FOR RAMROD

"Then did I see in the whole work of GOD, that a man is not able to find out the work that is done under the sun, inasmuch as though a man were able to toil to seek for it he would not find it, and even if he were wise to think to know it, he would yet not be able to find it" [Eccl viii 17].

This chapter discusses aspects of real-time operating systems which must be considered when providing the supervisory control required by Ramrod. In order to meet the objectives of speed and reliability it was decided to place as much as possible of the operating system in hardware rather than in software. Finally in order to meet the criterion of reliability, it was decided to distribute the operating system as tar as possible throughout Ramrod.

### 3.1 The Role of an Operating System

of transforming raw hardware into a system more amenable to its users! In addition, it should make the best possible use of available hardware so as to be generally more cost-effective.

An operating system has to be able to:

- Provide maximum system reliability with a minimum of operator interventio .

- 2. Exclude the user from details of implementation i.e make the system appear to the user as simple as possible.

- 3. Give the impression that the user has the sole use of the computer.

In general then a real-time, multi-user operating system should be able to:

- Perform input/output either to a peripheral

and/or to a user

- 2. Dispatch tasks to processors according to some predefined algorithm

- 3. Perform multitasking, i.e. allow many tasks to be executed concurrently

- 4. Supervise communications between tasks and/or the operating system

- 5. Recognize and service interrupts

# 3.2 Multiprocessor Operating Systems

In the system developed in this thesis, Ramrod, in which there are many slave processors available for executing tasks, the operating system has an extra function to perform in scheduling the slave processors for execution of tasks. Once a task is dispatched to a free slave processor then the slave processor still has to be initiated. This is a true multitasking of multiprocessing environment and tasks can be said to be running concurrently. It must be noted that concurrency in a parallel processor computer is true concurrency as processors can execute tasks absolutely simultaneously, whereas there is only 'apparent' concurrency in a uniprocessor computer (since the so-called concurrent tasks are actually being processed serially).

In order to have a near-linear increase in processing power in relation to an increase in processors, the master controller (in which the kernel of the operating system resides) should preferably have a cycle time faster than that of a single processor. This ensures the ability to control the slave processors as well as execute the kernel of the operating system.

An advantage of having some of the operating system removed from the processing environment is that the master can be faster than the slaves and thus have more effective control over the system. Secondly, a purpose-built hardware structure should be able to accommodate and execute the function of an operating system better than a general microprocessor. This is largely due to the fact that the actual functions performed by an operating system are relatively simple and require little data manipulation. The functions do, however, require to be executed as fast as possible, in order not to degrade the performance of the actual processors.

In order to have enough power to control many processors on the one hand and to contain an operating system on the other hand, bit-slice architecture (which is very fast and is microprogrammable, see app B), offers the opportunity of designing a purpose-built powerful operating system processor, as mentioned in 2.4.

An advantage of having some of the operating system removed from the processing environment is that the master can be faster than the slaves and thus have more effective control over the system. Secondly, a purpose-built hardward structure should be able to accommodate and execute the function of an operating system better than a general microprocessor. This is largely due to the fact that the actual functions performed by an operating system are relatively simple and require little data manipulation. The functions do, however, require to be executed as fast as possible, in order not to degrade the performance of the actual processors.

In order to have enough power to control many processors on the one hand and to contain an operating system on the other hand, bit-slice architecture (which is very fast and is microprogrammable, see app F), offers the opportunity of designing a purpose-built powerful operating system processor, as mentioned in 2.4.

### 3 3 The use of the Operating System in Ramrod

The Ramrod operating system has certain essential functions to perform. These are summarized as follows:-

- 1. Each processor in the Ramrod multiprocessor structure must be allocated a task to execute, and these have to be loaded into the common memory from an external source. A segment of memory must be assigned to each task, so that each processor can execute a task independently of other processors. A task is considered to be an activity which provides a function such as Input, Output or it may be an execution of a program, or segment of a program [LIST].

- 2. From 1 above it may be seen that each processor in Ramrod has to be allocated a time slice in order that it may access memory on the other side of the common bus. In addition, the particular memory segment selected has to be enabled. A processor must be able to address any or all of the memory segments in order that the system can be said to contain a virtual memory. To achieve this,

therefore, some sort of intelligent control is needed

- 3. A list of information pertaining to the location of defined tasks in memory, processors scheduled to run tasks, and the status of tasks must be monitored so that the operating system knows the configuration of the system at any point in time. An interface to the system user is also required in order that such system information may be accessed, as well as providing an overall ability to communicate with the system and its component parts.

- 4. In the event of a processor failing, the task which it had been executing must be redispatched to the next available working processor.

- 5. Some user-defined tasks will require the ability to communicate with others and this must be supervised in order that security of information may be assured. One processor may also need to draw on the results produced by another processor.

In view of the above more than dedicated logic is needed for the total control of the system. Therefore, an interligent master controller must be created which, in essence, contains some basic features of the kernel of an operating system, and may indeed implement these facilities in hardware (see 4.2.).

As has been pointed out in chapter 1, distribution of the hardware improves system reliability and similarly distribution of the operating system will improve software reliability. Thus it was decided to distribute the operating system as much as possible. The major effect of this is to provide for limited operation in the event of the failure of a particular section of the system.

# 3.4 Basic Structure of the Operating System.

It has successfully been shown that a hardware-based operating system implemented using bit slice technology can indeed work with a high degree of efficiency [ROD 76].

As was demonstrated in Roci's work the advantage of a high operating so to and requires a relatively simple hardware structur. This displicity aids in the displicity of the hardware/software structure. The core of an operating system is the executive or the nucleus, and it is this that will be impremented in the bit that with memory management, input/output, task dispatching, processor scheduling, inter-task communication and interrupt.

The operating system proposed for Ramrod also has the highly desirable property of being partially distributed. This increases the reliability of the system as a whole, because once a slave processor is executing a task, it needs no assistance from the master until inter-task communication is wanter or the task has communication is wanter or the task has communication occur. This feature is important in view of the strategic role of the operating system construction. Clearly as appendix Jahows, from the strategic role of the master should not cause a total system collapse. Therefore an effort should be made to distribute the operating system

wherever possible.

Thus routines related to the function of the Input/Output module are implemented in the slave processors while the rest of the kernel of the operating system is incorporated in the master bit-slice processor.

Another important consideration in the design of the operating system is the control over memory usage. Memory management is concerned with loading tasks into memory, ensuring that there is place for the task to reside and finally removing completed tasks. This can be combined in Ramrod with task dispatching since the memory is common to all processors, and therefore a particular memory segment can be assigned to any processor. A Task Control Block (TCB) table is kept to inform the nucleus where the task resider the state of the task and to which processor it has been dispatched. Thus dynamic rescheduling is achieved by allowing another free slave processor access to the segment of memory.

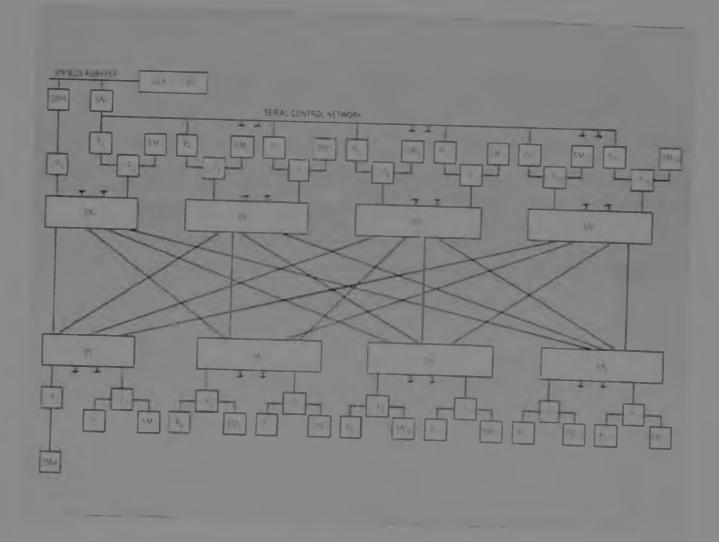

Pairing a memory segment and a slave processor is accomplished by selection, by the master, of a segment of memory simultaneously with the selection of a processor for access on the TDM common bus. A modulo n counter (where n = number of processors) generates consecutive addresses for reading a fast Read/Write memory (RAM), whose output selects or deselects processors and memory segments. The master controller has the ability to rewrite this fast RAM, thus allowing any combination of processor-memory communication. This is illustrated in figure 3.1, which shows that the master controller determines which devices are allowed access onto the TDM bus.

FIGURE 3.1 SLAVE PROCESSOR TO MEMORY SEGMENT PAIRING

## 3.5 Inter-Process Communications

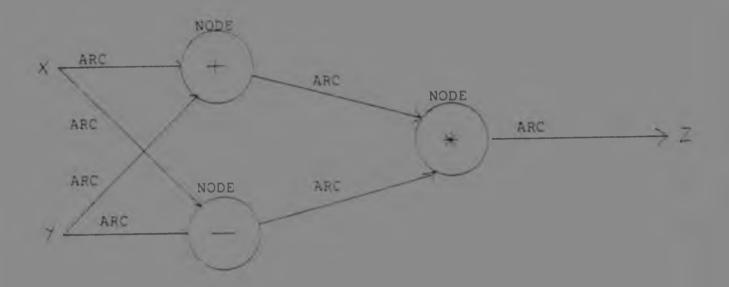

In any system in which several tasks are being executed in parallel the situation will always occur when processors require to exchange data. Inter-process communication can be defined, in this context, as message passing between processes. For example, in a simple arithmetic calculation Z = (X+Y) \* (X-Y), one task could do the addition, a second task the subtraction and a third task the multiplication. The first two tasks have to pass their data to the third task, in order that the multiplication of occ. Thus the third task waits until it receives sages from task 1 and task 2. Inter-process communication (IPC) has to be co-ordinated by the operating system which must know, amongst other things, who the partners to the message are, so that processes can cooperate correctly in the manipulation of data. Whilst a more detailed discussion of communications appears in Chapter 6, the discussion which follows outlines how Inter Process Communication (IPC) is presently implemented in Ramrod.

Of importance in the consideration of IPC methodology is the danger of deadlocks. This arises because resources are usually allocated to processors on the basis of their availability without any predetermined allocation algorithm. Deadlock can be explained as in

the following example: A user task is granted the printer for outputing data and then requests the card reader to read in data; Another user task is using the card reader and then requests the printer so that it can output results. If these resources can only be used by one process at a time, and neither process will release the resource it holds, then deadlock occurs. In order to prevent deadlock, (or "deadly embrace") Dijkstra proposed the semaphore[DIJ], as 'a non negative integer, which apart from initialisation of its value, can be acted upon only by the operations wait and Signal' [LIS]. The Wait and Signal functions can be summarized as follows;

Wait(s) : when s>0, decrement s

Signal(s): increment s

Thus a resource (printer etc) can only be allocated to one process. This approach is widely used and could be implemented in Ramrod (see section 6.3).

Another more practical solution is, however, possible.

If a program is partioned into tasks, which are executed sequentially, such that there is no need for any inter-task communications until a task is terminated, and inter-task communication only takes place between adjacent tasks, then deadlock can never

occur! Thus when partitioning the program, if a point in a task is reached where communication with another task is needed, this is the place where the user should partition the program (see 6.2).

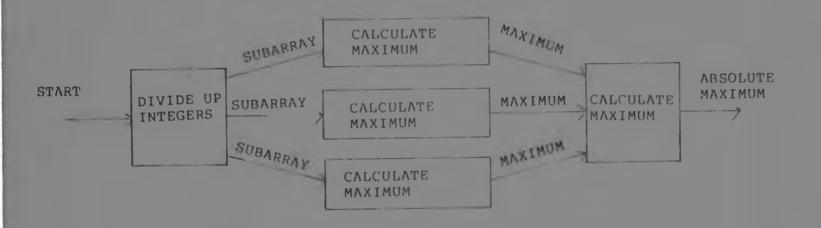

It is suggested that the user, who writes the programs for his particular needs should do the partitioning of the tasks in this manner. This clearly is possible to implement automatically but it is beyond the scope of this present investigation to include software which will partition the tasks according to the above specification. In the present system this is carried out manually. Thus using data flow techniques (chapter 6) the only communication between one task and another occurs either at the beginning or at the end of the task. This highly pragmatic approach proved most useful, and suprisingly easy to implement. It is however only a partial and somewhat crude solution. As will be discussed in the next section, Ramrod has provided many other possible hardware mechanisms which may be used to implement Inter-Process Communication. Thus Ramrod is a useful testbed for evaluating a variety of proposals.

## 3.5.1 Communication mechanisms provided by Ramrod

Ramrod provides three mechanisms through which tasks can communicate with each other.

- 1. An intelligent Input/Output controller

(Ethernet see appendix E), which allows any

processor to be connected to any peripheral,

or to any other processor.

- 2. A vector interrupt system to the master: A task can suspend itself once IPC is required and be woken up at a later stage. This is analogous to Hoare's communicating sequential processes (see chapter 6).

- Tasks communicate by passing data through common memory (see earlier discussion on ojikstra's semaphores, which can be implemented via this mechanism).

However it must be pointed out that the above are only mechanisms, and do not provide for deadlock avoidance!

They do show however the power of the structure of Ramrod as an experimental tool.

## 3.6 User Task to Operating System Communication

Communication between any user task and the operating system is effected simply by means of a 'watchdog' timeout signal which interrupts the master controller. A task must contain instructions which continuously trigger a monostable multivibrator, which will time out if the task terminates or if a failure occurs. The interrupts of the slave processors are vectored so that the master can identify the interrupt. The master can then check whether the timeout was caused by a processor fault or task fault or if the processor has finished executing the task.

In summary this simple mechanism is extremely powerful and provides both for a termination indication, as well as the ability to detect a processor failure.

#### 3.7 Conclusion

Implementing the operating system in hardware (by purpose designed architecture ) makes the overall system reliable and flexible, because (as stated before) hardware is naturally more reliable than software. In addition there is an ability to microprogram the operating system, it is claimed that the system is flexible, as the architecture is easily

modified to suit the user's needs. The operating system functions have to be complemented by the minimal amount of software and this adds to reliabilty.

Furthermore the operating system is distributed in that Input/Output and certain local control routines are implemented in the slave processors. Thus the reliability of the system as a whole is enhanced.

#### CHAPTER 4

#### SYSTEM HARDWARE

"No man hath control over the spirit; and there is no control over the day of death; and there is no representation in that war; and wickedness will not deliver those that practised" [Eccl viii 8].

The block diagram of Ramrod was discussed in 2.6 and in this chapter the hardware of both the bit-slice master processor and the multiprocessors are outlined. A more detailed discussion of this hardware structure is to be found in appendix G.

In order for any new architecture to have economic relevance, it must be simple and efficient, and meet the needs of its potential users. In order to achieve these aims it should exhibit such features as fault-tolerance and provision of the neccessary redundancy. The multiprocessor tructure of Ramrod fulfills these criterea.

## 4.1 System Overview

As has been discussed previously (sect. 1.5), distribution of work over veral conventional processors with common storage is one approach to increasing processing speed. However, a serious problem with common, shared-memory multiprocessor systems is that all the memory is accessible by all processors, and therefore special support is required to ensure that processors do not access the same address simultaneously, thereby corrupting each other's data [AGER 82].

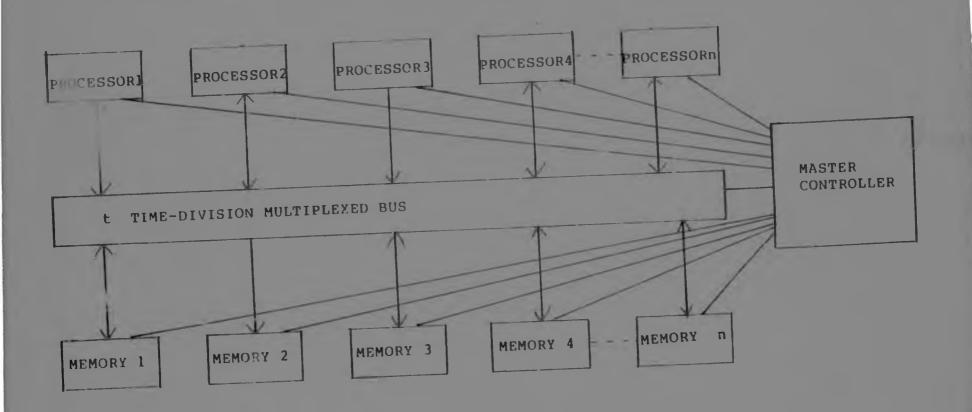

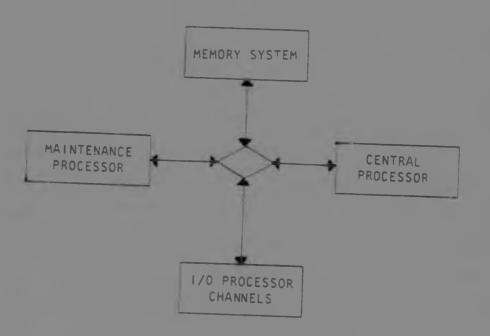

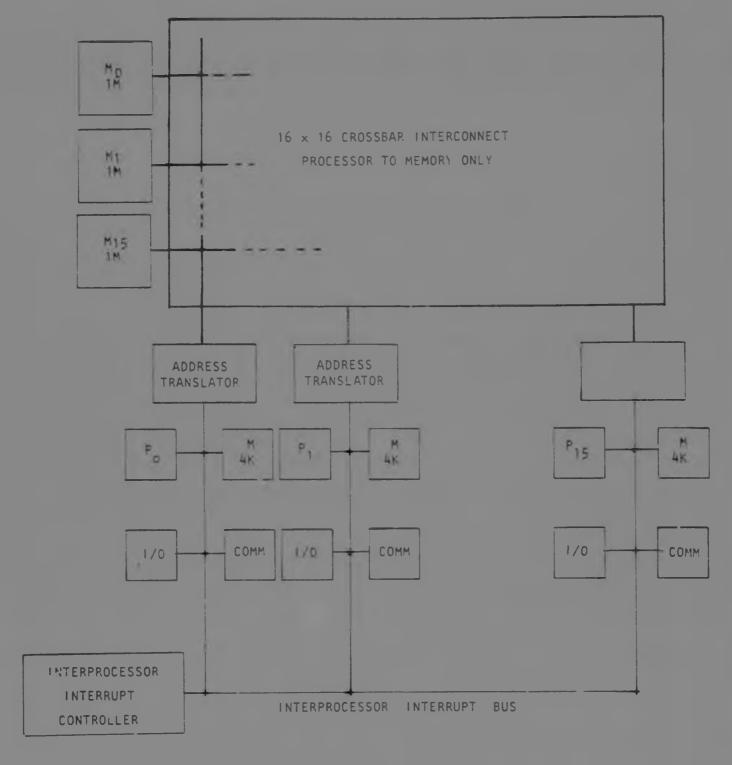

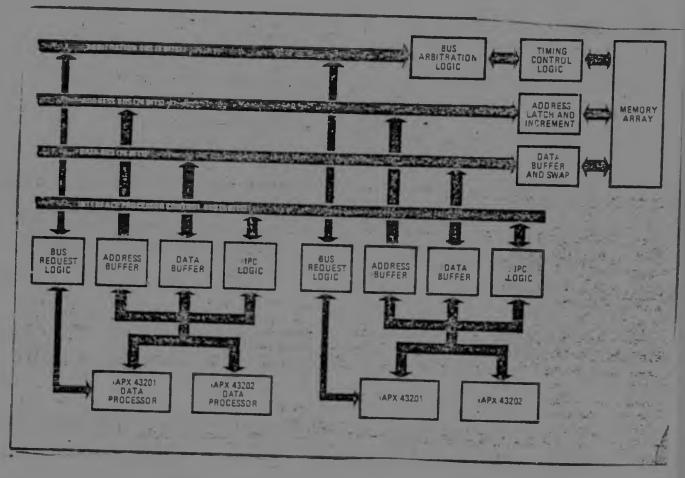

Figure 4.1 shows the overall system block diagram with the Master Controller (MC) which is in charge of the system. The MC which is a bit slice hardware rased real time operating system controls the data/address latches on both sides of the Time Division Multiplexed (TDM) bus. As the latches are identical the hardware can be said to be modular.

FIGURE 4.1 RAMROD BLOCK DIAGRAM

The multiprocessor architecture proposed and designed makes use of conventional microprocessors, with their relatively slow processing times. Of great significance is the fact that the cycle time of a single processor in the system is not significantly decreased by the processor-memory switch. The . average cycle time for a conventional microprocessor is approximately 1 microsecon1, tl 'me being set primarily by speed of memory access. Figure 4.2 shows how all the processors communicate with the common memory by way of the TDM bus. While the memory is being accessed the bus is idle w.r.t use by the first processor and this time is available for use by the other processors. Each processor uses the bus for a very short period and if there are 50 processors then this period is 20 nanoseconds. Thus with the present system 50 microprocessors are able to communicate with each other with almost no degradation in performance of any of the microprocessors.

ADDRESS TO MEMORY (PROCESSOR 1)

FIGURE 4.2 TIMING ON THE SHARED BUS

The cyclic operation occurs as follows: each processor deposits data and addresses into its latches and when these are given access to the bus, data are transfered into latches on the other side of the bus.

It should be noted that the data can be sent to more than one set of memory latches, thus giving the processors access to more than one memory segment simultaneously. In addition it should be noted that the concept of a distributed data base can be implemented easily on this type of computer system, as a global variable with many copies can be simultaneously updated by one processor. A distributed data base implies that each processor in the system has its own copy of the data base.

#### 4.2 Basic Structure of Ramrod

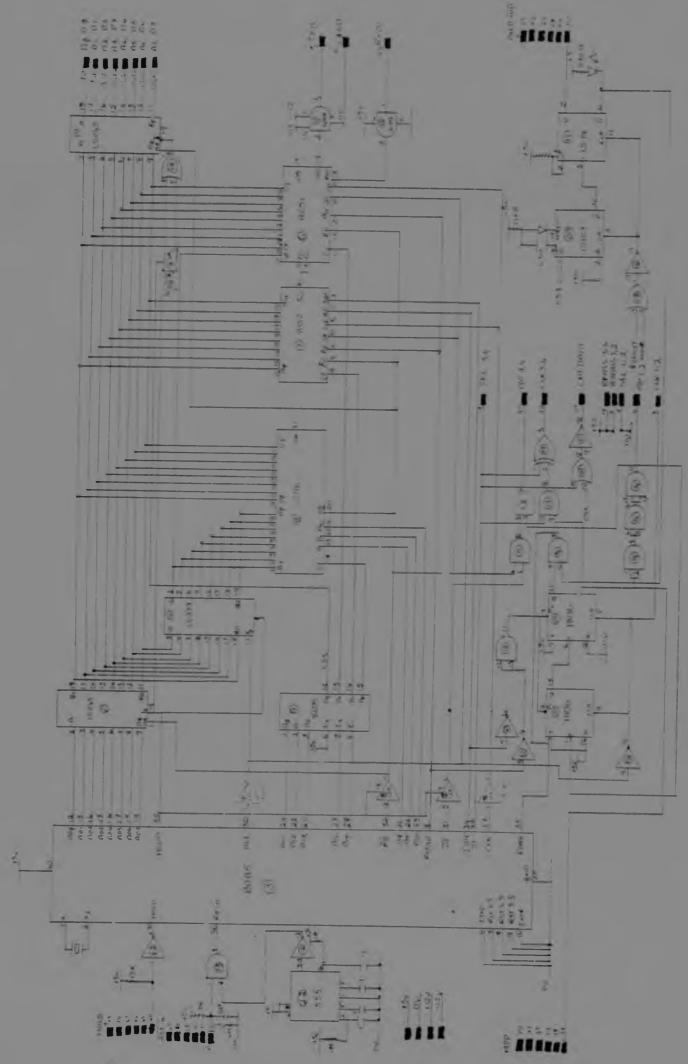

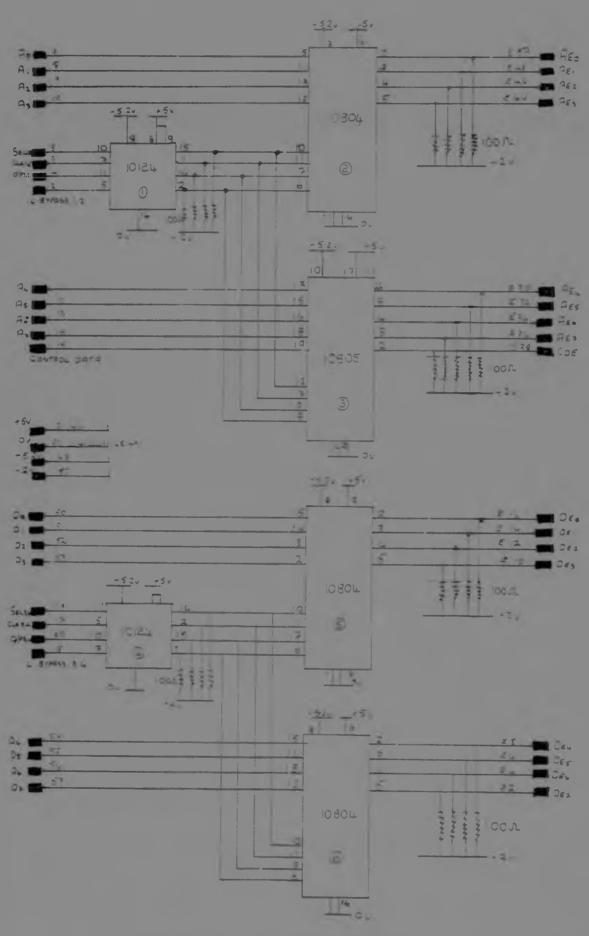

The following section provides an everview of the various components of Ramrod. Full details of actual implementation, with the circuit diagrams, appear in Appendix G.

### 4.2.1 Microprocessor Module

The microprocessor slave module consists of an 8.385 microprocessor together with memory and the associated support chips. It is also provided with a serial data channel to allow access during devel. Onto (so that a terminal could be provided to each slave processor and hence allow direct control).

These slave processors have to be synchronised with the Time-Division Multiplexed (TDM) bus in order that there should be a minimal amount of processor idle time (as discussed in sction 2.4.3). In addition, in order that the ocating system can be distributed, a limited number occurring system functions must be present on each processor (so that failure of the master controller is not critical in the short term). The slave processors can therefore continue executing the take dispatched to them until the tasks suspend themselves, and thus the system can "gracefully degrade".

The local operating system is implemented in a resident Electronically Programmable Read Only Memory (EPROM) on the slave processor module and includes additional software to enable the slave to be self-tested.

#### 4.2.2 <u>TDM bus and Interface</u>

The system designed is tolerant of processor failure but, as with the conventional common bus, it is very sensitive to bus failure. A catastrophic failure occurs if the bus fails and therefore a dual, redundant bus must be provided to minimize the possibility of system failure due to bus failure. The system can contain two sets of identical latches for each processor and memory segment. Thus, when one bus fails (which can be detected by the master processor), its associated latches are disabled and the second set of latches is enabled. A second control board (see 4.2.7.8) can achieve this switching of latches.

Most Multiprocesor systems with a common memory and bus suffer from bandwidth limitations, since the bus bandwidth will not increase even though more processors are added (as has been mentioned previously in section 2.2.1). Thus, what is needed is a state-of-the-art design, capable of high speeds of transfer, inexpensive and uncomplicated.

When choosing a logic family for the implementation of the bus and interface there are several factors to consider: i.e. noise immunity, logic flexibility, speed and some practical considerations. Obviously, for each application the factors must have a certain priority. In the case of the bus controller the highest priority is given to speed, as this determines the transfer rate across the bus. Then the priorities are: logic flexibility, practical considerations and noise immunity.

## 4.2.2.1 Speed -

In order to decrease the degradation in processor performance, the transfer rate of the bus must be high. Unfortunately the faster the logic, the higher the cost and the power dissipation! When considering high speed, the number of levels of gating becomes an added factor, which in turn is a function of the logic flexibility.

Gate propogation delay is perhaps the most important measure of speed. It is defined as the time taken for an output to appear from a gate after the signal has been entered at the input.

#### 4.2.2.2 Logic Floxibility -

Reduction of the component count for a particular device is dependant on the flexibility of the logic family used. Flexibility is roughly related to the number of different outputs the integrated circuit (IC) has available. Wire-ORing, the capability of tying more than one output together also significantly reduces component count. Other factors to consider are:

- 1. Complementary output, and that Invertery prounneccesary.

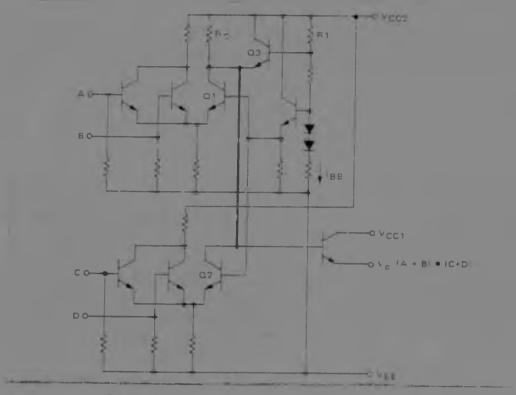

- 2. It driving capability, because the faster the signal the more closely a short line acquires the characteristics of a transmission line [MOT B].