# Sparse Array Representations And Some Selected Array Operations On GPUs

Hairong Wang School of Computer Science University of the Witwatersrand

A dissertation submitted to the Faculty of Science, University of the Witwatersrand, Johannesburg, in fulfilment of the requirements for the degree of Master of Science.

Supervisor: Professor Ekow Otoo

July 2014, Johannesburg

# Declaration

I, Hairong Wang, hereby declare that this dissertation is my own, unaided work. It is being submitted for the Degree of Master of Science at the University of the Witwatersrand, Johannesburg. It has not been submitted before for any degree or examination at any other university.

Signature of candidate:\_\_\_\_\_

<u>28th</u> day of July 20 <u>14</u> in Johannesburg .

### Abstract

A multi-dimensional data model provides a good conceptual view of the data in data warehousing and On-Line Analytical Processing (OLAP). A typical representation of such a data model is as a multi-dimensional array which is well suited when the array is dense. If the array is sparse, i.e., has a few number of non-zero elements relative to the product of the cardinalities of the dimensions, using a multi-dimensional array to represent the data set requires extremely large memory space while the actual data elements occupy a relatively small fraction of the space. Existing storage schemes for Multi-Dimensional Sparse Arrays (MDSAs) of higher dimensions k (k > 2), focus on optimizing the storage utilization, and offer little flexibility in data access efficiency. Most efficient storage schemes for sparse arrays are limited to matrices that are arrays in 2 dimensions. In this dissertation, we introduce four storage schemes for MDSAs that handle the sparsity of the array with two primary goals; reducing the storage overhead and maintaining efficient data element access. These schemes, including a well known method referred to as the Bit Encoded Sparse Storage (BESS), were evaluated and compared on four basic array operations, namely construction of a scheme, large scale random element access, sub-array retrieval and multi-dimensional aggregation. The four storage schemes being proposed, together with the evaluation results are: i.) The extended compressed row storage (xCRS) which extends CRS method for sparse matrix storage to sparse arrays of higher dimensions and achieves the best data element access efficiency among the methods compared; ii.) The bit encoded xCRS (BxCRS) which optimizes the storage utilization of xCRS by applying data compression methods with run length encoding, while maintaining its data access efficiency; iii.) A hybrid approach (Hybrid) that provides the best control of the balance between the storage utilization and data manipulation efficiency by combining xCRS and BESS. iv.) The PATRICIA trie compressed storage (PTCS) which uses PATRICIA trie to store the valid non-zero array elements. PTCS supports efficient data access, and has a unique property of supporting *update* operations conveniently. v.) BESS performs the best for the multi-dimensional aggregation, closely followed by the other schemes.

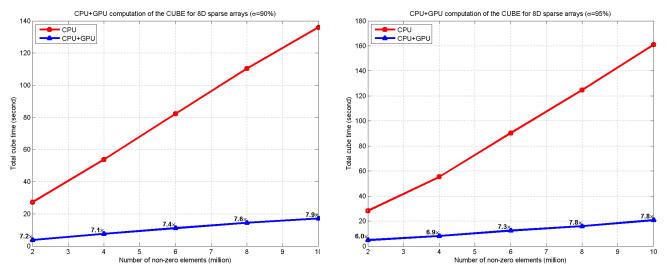

We also addressed the problem of accelerating some selected array operations using General Purpose Computing on Graphics Processing Unit (GPGPU). The experimental results showed different levels of speed up, ranging from 2 to over 20 times, on large scale random element access and sub-array retrieval. In particular, we utilized GPUs on the computation of the *cube* operator, a special case of multi-dimensional aggregation, using BESS. This resulted in a 5 to 8 times of speed up compared with our CPU only implementation. The main contributions of this dissertation include the developments, implementations and evaluations of four efficient schemes to store multi-dimensional sparse arrays, as well as utilizing massive parallelism of GPUs for some data warehousing operations.

# Acknowledgements

First of all, I would like to thank my research supervisor, Professor Ekow Otoo, not only for his excellent guidance during the course of my research work, but also for the ideas he suggested, and his patient revision of my dissertation. My special thanks also go to Professor Michael Sears for his help and support.

I am grateful to the National Research Foundation (NRF) South Africa for their financial support for my study.

Finally, I would like to thank my husband, Sheng, for his love and support; and my three lovely daughters, Nandi, Christine and Marilyn, for being the joy of my life.

# Contents

|    |         | Declaration                                         |    |  |  |  |  |  |

|----|---------|-----------------------------------------------------|----|--|--|--|--|--|

|    |         | Abstract                                            | ii |  |  |  |  |  |

|    |         | Acknowledgements                                    | ii |  |  |  |  |  |

| Li | st of l | <b>`igures</b> v                                    | ii |  |  |  |  |  |

| Li | st of ] | Yables vi                                           | ii |  |  |  |  |  |

| Li | st of A | lgorithms vi                                        | ii |  |  |  |  |  |

| 1  | Intr    | oduction                                            | 1  |  |  |  |  |  |

|    | 1.1     | Problem Motivation                                  | 1  |  |  |  |  |  |

|    | 1.2     | Problem Statement                                   | 2  |  |  |  |  |  |

|    | 1.3     | Overview of Some Known Approaches                   | 4  |  |  |  |  |  |

|    | 1.4     | Overview of Our Solution                            | 5  |  |  |  |  |  |

|    | 1.5     | Main Contributions                                  | 7  |  |  |  |  |  |

|    | 1.6     | Organization of the Dissertation                    | 8  |  |  |  |  |  |

| 2  | Bac     | ground and Related Work                             | 9  |  |  |  |  |  |

|    | 2.1     | Storage Schemes for Multi-Dimensional Sparse Arrays | 9  |  |  |  |  |  |

|    |         | 2.1.1 Index-Value Pair                              | 0  |  |  |  |  |  |

|    |         | 2.1.2 Offset-Value Pair                             | 1  |  |  |  |  |  |

|    |         | 2.1.3 Bit Encoded Sparse Storage                    | 2  |  |  |  |  |  |

|    |         | 2.1.4 Compressed Row or Column Storage              | 3  |  |  |  |  |  |

|    | 2.2     | Data Warehousing and OLAP                           | 4  |  |  |  |  |  |

|    | 2.3     | Multi-Dimensional Aggregation                       | 6  |  |  |  |  |  |

|    |         | 2.3.1 The CUBE                                      | 7  |  |  |  |  |  |

|    |         | 2.3.1.1 Search Lattice                              | 9  |  |  |  |  |  |

|    |         | 2.3.1.2 Algorithms for Computing the CUBE           | 0  |  |  |  |  |  |

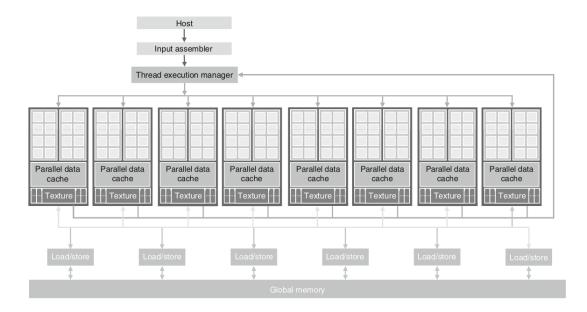

|    | 2.4     | General Purpose Computing Using GPUs 2              | 2  |  |  |  |  |  |

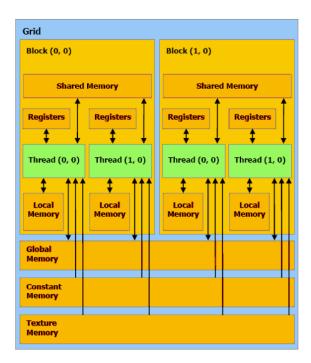

|    |         | 2.4.1 GPU Architecture                              | 3  |  |  |  |  |  |

|   |                                      | 2.4.2   | CUDA Programming Model                                                   | 24 |

|---|--------------------------------------|---------|--------------------------------------------------------------------------|----|

|   | 2.5                                  | Applic  | ation of GPUs to Data Warehousing                                        | 26 |

| 3 | Mul                                  | ti-Dime | nsional Sparse Array Representations                                     | 28 |

|   | 3.1                                  | Metho   | dology                                                                   | 28 |

|   | led Compressed Row or Column Storage | 29      |                                                                          |    |

|   |                                      | 3.2.1   | XCRS and Its Construction                                                | 30 |

|   |                                      | 3.2.2   | Random Element Access and Sub-Array Retrieval in xCRS                    | 31 |

|   |                                      | 3.2.3   | Space Utilization of xCRS                                                | 33 |

|   | 3.3                                  | Bit En  | coded Extended Compressed Row Storage                                    | 33 |

|   |                                      | 3.3.1   | Word-Aligned Hybrid Code                                                 | 33 |

|   |                                      | 3.3.2   | BxCRS and Its Construction                                               | 34 |

|   |                                      | 3.3.3   | Random Element Access and Sub-Array Retrieval in BxCRS                   | 36 |

|   | 3.4                                  | Hybrid  | Approach                                                                 | 38 |

|   |                                      | 3.4.1   | Hybrid and Its Construction                                              | 38 |

|   |                                      | 3.4.2   | Random Element Access and Sub-Array Retrieval in Hybrid                  | 39 |

|   |                                      | 3.4.3   | Some Properties of Hybrid                                                | 40 |

|   |                                      |         | 3.4.3.1 The Storage Overhead                                             | 40 |

|   |                                      |         | 3.4.3.2 The Time Complexities of Random Element Access and Sub-Array Re- |    |

|   |                                      |         | trieval in Hybrid                                                        | 40 |

|   | 3.5                                  | PATRI   | CIA Trie Compressed Storage                                              | 41 |

|   |                                      | 3.5.1   | PATRICIA                                                                 | 41 |

|   |                                      | 3.5.2   | PTCS and Its Key                                                         | 42 |

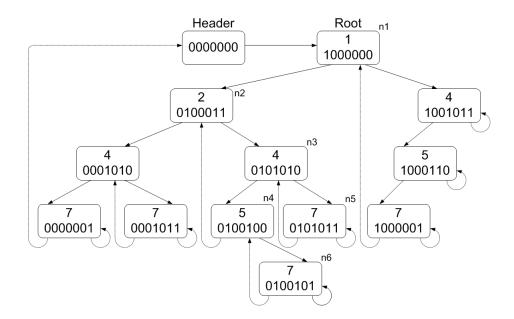

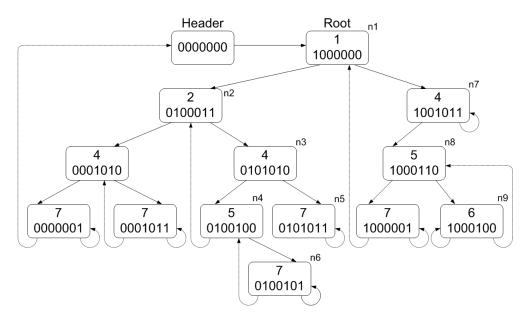

|   |                                      | 3.5.3   | PTCS Construction                                                        | 43 |

|   |                                      | 3.5.4   | Random Element Access and Sub-Array Retrieval in PTCS                    | 46 |

|   |                                      | 3.5.5   | Some Properties of PTCS                                                  | 47 |

| 4 | Mul                                  | ti-Dime | nsional Aggregations of Sparse Array Elements                            | 48 |

|   | 4.1                                  | Aggreg  | gation Using PTCS and BESS                                               | 49 |

|   | 4.2                                  | Aggreg  | gation Using xCRS and BxCRS                                              | 50 |

|   | 4.3                                  | Aggreg  | gation Using Hybrid                                                      | 51 |

|   | 4.4                                  | Compa   | arative Analysis of Computing Aggregations Using Various Schemes         | 52 |

|   | 4.5                                  | Compu   | uting the Cube                                                           | 53 |

|   |                                      | 4.5.1   | Paths in the Search Lattice                                              | 54 |

|   |                                      | 4.5.2   | Computing the CUBE Using BESS                                            | 56 |

|   |                                      | 4.5.3   | Computing the CUBE Using PTCS                                            | 58 |

| 5 | Selected Array Operations on GPUs |                    |             |                                                       |    |  |  |

|---|-----------------------------------|--------------------|-------------|-------------------------------------------------------|----|--|--|

|   | 5.1                               | Overv              | iew         |                                                       | 59 |  |  |

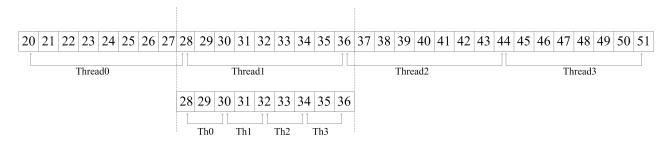

|   | 5.2                               | Large              | Scale Ran   | dom Element Access                                    | 61 |  |  |

|   | 5.3                               | Sub-A              | rray Retrie | eval                                                  | 62 |  |  |

|   | 5.4                               | Comp               | uting The   | Cube                                                  | 65 |  |  |

|   |                                   | 5.4.1              | Resetting   | g the Attribute Order                                 | 65 |  |  |

|   |                                   | 5.4.2              | Sorting     |                                                       | 66 |  |  |

| 6 | Exp                               | eriment            | tal Setup   |                                                       | 68 |  |  |

|   | 6.1                               |                    | -           | wironment                                             | 68 |  |  |

|   | 6.2                               | Experi             | imental Da  | uta                                                   | 68 |  |  |

| _ | <b>D</b>                          |                    |             |                                                       | -1 |  |  |

| 7 |                                   |                    | e Evaluat   |                                                       | 71 |  |  |

|   | 7.1                               |                    |             | on of Various Storage Schemes                         |    |  |  |

|   | 7.2                               | · ·                |             | esults and Comparative Analyses                       |    |  |  |

|   |                                   | 7.2.1              |             | on CPU Only Processing                                |    |  |  |

|   |                                   |                    | 7.2.1.1     | Performance of Storage Scheme Construction            |    |  |  |

|   |                                   |                    | 7.2.1.2     | Performance of Large Scale Random Element Access      |    |  |  |

|   |                                   |                    | 7.2.1.3     | Performance of Sub-Array Retrieval                    |    |  |  |

|   |                                   |                    | 7.2.1.4     | Performance of Aggregation                            |    |  |  |

|   |                                   |                    | 7.2.1.5     | Performance of Computing the CUBE Using PTCS and BESS |    |  |  |

|   |                                   | 7.2.2              |             | on CPU+GPU Co-Processing                              |    |  |  |

|   |                                   |                    | 7.2.2.1     | Performance of Large Scale Random Element Access      |    |  |  |

|   |                                   |                    | 7.2.2.2     | Performance of Sub-Array Retrieval                    |    |  |  |

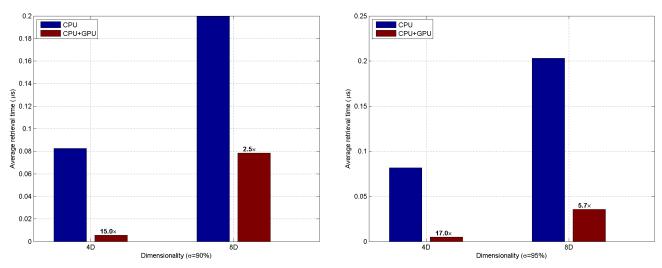

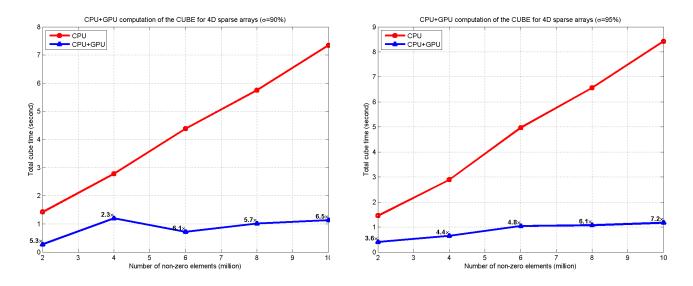

|   |                                   |                    | 7.2.2.3     | Performance of Computing the CUBE Using BESS          | 80 |  |  |

| 8 | Con                               | clusion            |             |                                                       | 87 |  |  |

|   | 8.1                               | Main (             | Objectives  |                                                       | 87 |  |  |

|   | 8.2                               | Main Contributions |             |                                                       |    |  |  |

|   | 8.3                               | Future             | Work        |                                                       | 89 |  |  |

|   | Арр                               | endix              |             |                                                       | 90 |  |  |

| A | Add                               | itional .          | Algorithn   | 15                                                    | 90 |  |  |

|   | A.1                               | The Su             | ıb-Array F  | Retrieval Algorithm in XCRS                           | 90 |  |  |

|   | A.2                               | The A              | lgorithm to | o Search the Array <i>compwrd</i>                     | 91 |  |  |

|   | A.3                               | The Su             | ub-Array F  | Retrieval Algorithm in PTCS                           | 92 |  |  |

# **List of Figures**

| 2.1  | An Example of an MDSA                                                                                    | 11 |

|------|----------------------------------------------------------------------------------------------------------|----|

| 2.2  | The Aggregation on a 3-Dimensional Array                                                                 | 17 |

| 2.3  | The Aggregation on the Group-By of a Single Dimension                                                    | 18 |

| 2.4  | A Search Lattice with 4 Attributes                                                                       | 19 |

| 2.5  | A Modern NVIDIA GPU Architecture                                                                         | 24 |

| 2.6  | CUDA Memory Hierarchy                                                                                    | 26 |

| 3.1  | The Process of Bitmap Compressing                                                                        | 35 |

| 3.2  | An Example of a PATRICIA Trie                                                                            | 42 |

| 3.3  | A PTCS Key Structure                                                                                     | 43 |

| 3.4  | The Insertion of a Key Into a PATRICIA Trie                                                              | 44 |

| 4.1  | Aggregating the MDSA Represented in PTCS or BESS                                                         | 50 |

| 5.1  | An Example of P-Ary Search                                                                               | 62 |

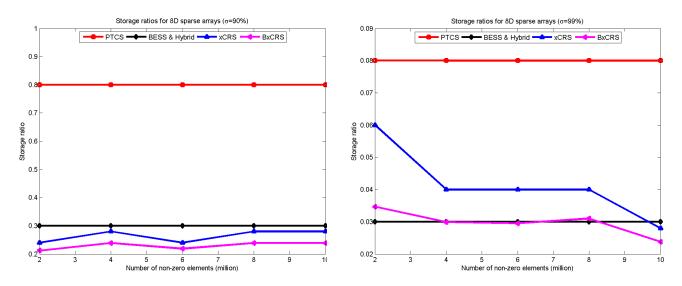

| 7.1  | Storage Ratios for the 8-Dimensional Sparse Arrays                                                       | 72 |

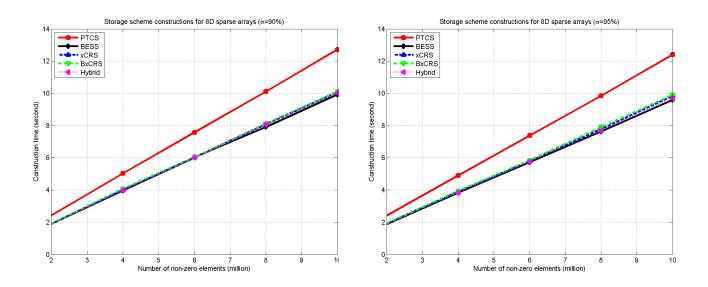

| 7.2  | The Construction Time of Various Storage Schemes                                                         | 73 |

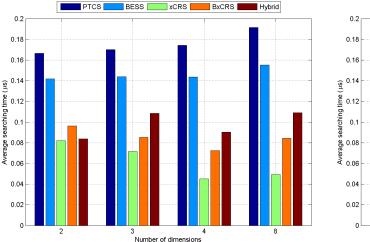

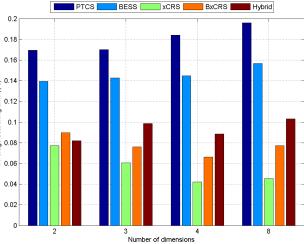

| 7.3  | The Average Random Element Access Time of Various Storage Schemes                                        | 74 |

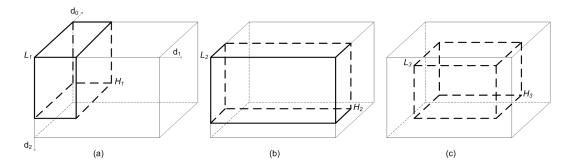

| 7.4  | The Structures of the Sub-Arrays to be Retrieved                                                         | 75 |

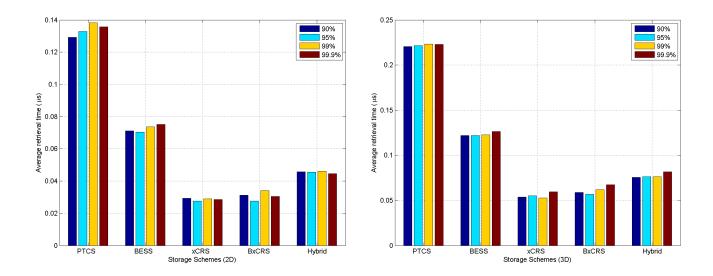

| 7.5  | The Average Sub-Array Retrieval Time of Various Storage Schemes $(k = 2 \text{ and } k = 3) \dots$       | 77 |

| 7.6  | The Average Sub-Array Retrieval Time of Various Storage Schemes $(k = 4 \text{ and } k = 8) \dots$       | 77 |

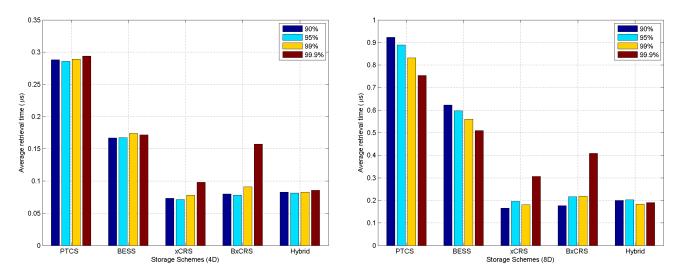

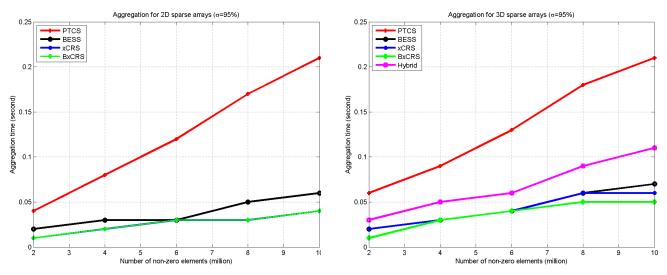

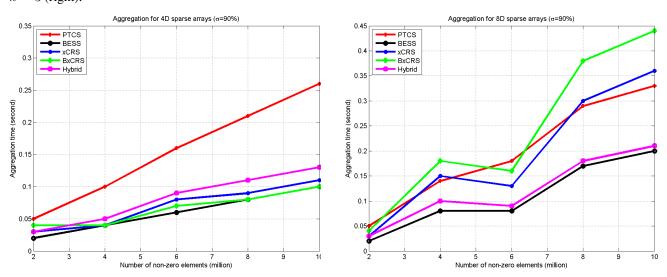

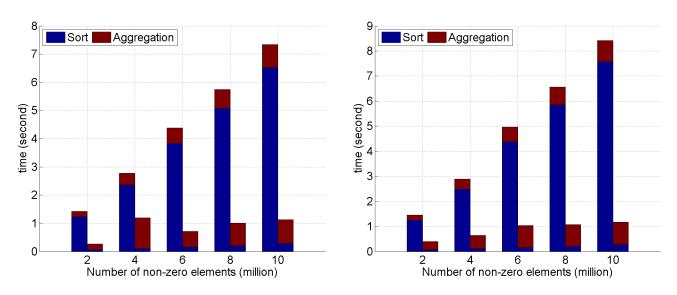

| 7.7  | The Multi-Dimensional Aggregation Time of Various Storage Schemes $\left(k=2 \text{ and } k=3\right)$ .  | 81 |

| 7.8  | The Multi-Dimensional Aggregation Time of Various Storage Schemes $\left(k=4 \text{ and } k=8\right)$ .  | 81 |

| 7.9  | The Multi-Dimensional Aggregation Time of Various Storage Schemes $\left(k=4 \text{ and } k=8\right)$ .  | 81 |

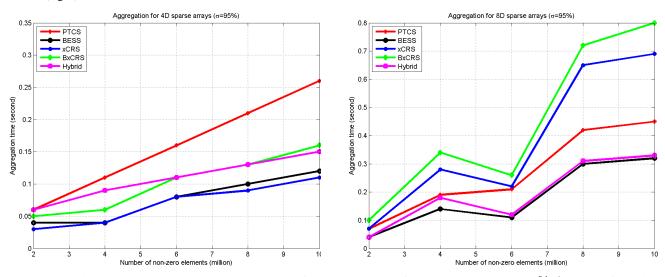

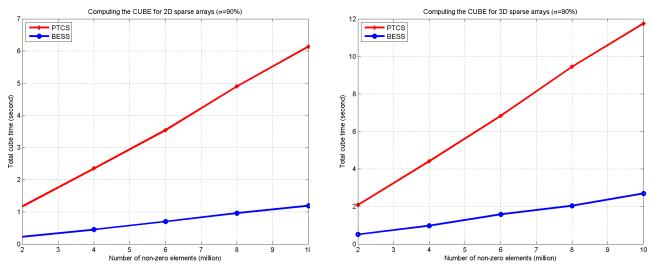

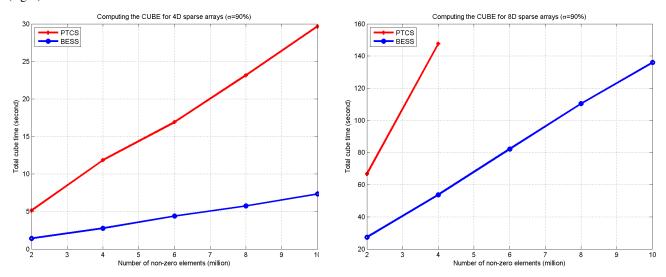

| 7.10 | The Time for Computing the Cube Using PTCS and BESS ( $k = 2$ and $k = 3$ )                              | 82 |

| 7.11 | The Time for Computing the Cube Using PTCS and BESS $(k = 4 \text{ and } k = 8) \dots \dots \dots \dots$ | 82 |

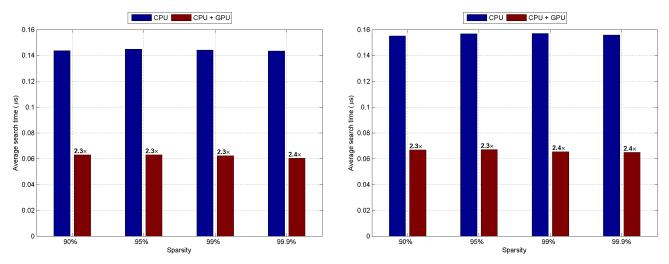

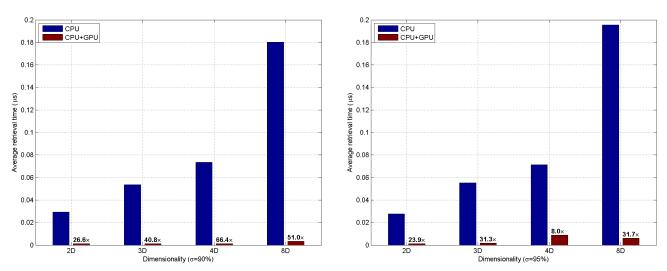

| 7.12 | The Average CPU+GPU Random Element Access Time Using BESS                                                | 83 |

| 7.13 | The Average CPU+GPU Random Element Access Time Using xCRS                                                | 83 |

| 7.14 | The Average CPU+GPU Random Element Access Time Using Hybrid                                              | 83 |

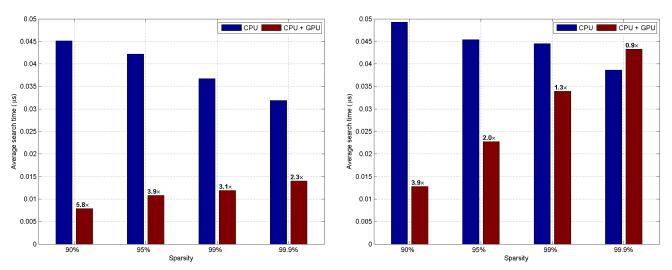

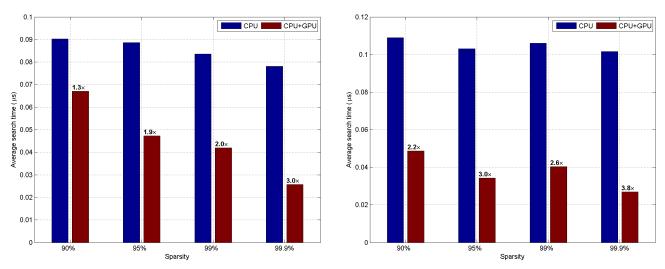

| 7.15 | The Average CPU+GPU Sub-Array Retrieval Time Using BESS                                                  | 84 |

| 7.16 | The Average CPU+GPU Sub-Array Retrieval Time Using xCRS                   | 84 |

|------|---------------------------------------------------------------------------|----|

| 7.17 | The Average CPU+GPU Sub-Array Retrieval Time Using Hybrid                 | 84 |

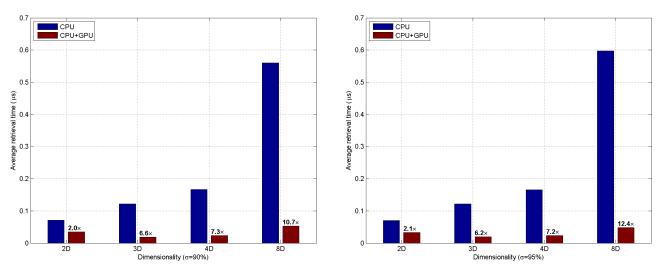

| 7.18 | The CPU+GPU Time for Computing the Cube Using BESS $(k = 4)$              | 85 |

| 7.19 | The CPU+GPU Time for Computing the Cube Using BESS $(k = 8)$              | 85 |

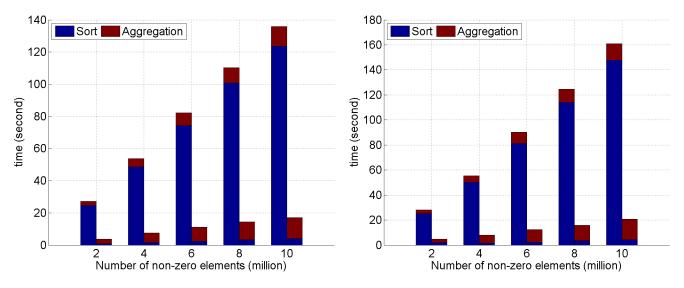

| 7.20 | The Sort and Aggregation Time for Computing the Cube Using BESS $(k = 4)$ | 86 |

| 7.21 | The Sort and Aggregation Time for Computing the Cube Using BESS $(k = 8)$ | 86 |

# **List of Tables**

| 2.1 | The Parameters and Notations                     | 10 |

|-----|--------------------------------------------------|----|

| 2.2 | An Example of Index-Value Pair Representation    | 11 |

| 2.3 | An Example of Offset-Value Pair Representation   | 12 |

| 2.4 | An Example of BESS Representation                | 13 |

| 2.5 | An Example of CRS                                | 14 |

| 3.1 | An Example of XCRS                               | 31 |

| 3.2 | An Example of BxCRS                              | 36 |

| 3.3 | An Example of Hybrid                             | 39 |

| 3.4 | The PTCS Key-Value Pair                          | 43 |

| 4.1 | The Costs of Computing Multiple Aggregations     | 53 |

| 6.1 | The Specifications of a Set of Experimental Data | 70 |

# **List of Algorithms**

| 1  | XCRS Construction                          | 31 |

|----|--------------------------------------------|----|

| 2  | XCRS Random Element Access                 | 32 |

| 3  | Compressing the Bitmap                     | 35 |

| 4  | BxCRS Random Element Access                | 37 |

| 5  | PTCS Construction                          | 45 |

| 6  | PTCS Random Element Access                 | 46 |

| 7  | Computing the Paths in a Search Lattice    | 56 |

| 8  | Computing the <i>Cube</i> Using BESS       | 57 |

| 9  | GPU P-Ary Search Algorithm                 | 63 |

| 10 | GPU Sub-Array Retrieval Using BESS         | 54 |

| 11 | Generating the Dimensional Data of an MDSA | 70 |

| 12 | XCRS Sub-Array Retrieval                   | 90 |

| 13 | Searching the Array <i>compwrd</i>         | 91 |

| 14 | PTCS Sub-Array Retrieval                   | 92 |

# **Chapter 1**

# Introduction

A multi-dimensional data model provides a good conceptual view of the data in data warehousing. This system supports On-Line Analytical Processing (OLAP) and facilitates complex analyses and visualizations of data. It enables finding certain patterns or trends in the data. Such valuable sources of information are essential in business management and decision making. Data warehouses usually contain historical, summarized and consolidated data, perhaps from several operational databases, over very long periods of time. They tend to be much larger than an individual operational database. The workloads are mostly complex queries that often need to access large amount of data and perform operations, such as scans and aggregations. As a result, the data in a data warehousing system is usually modeled as a multi-dimensional arrays [5]. For example, a data warehouse may represent business data (such as the sales data of a car manufacturer), medical data, scientific data and other real-world data. These data sets are characterized by several dimensions of interest and one or more measured values. Allied to the multi-dimensional data model is the multi-dimensional data cube, where the dimensions form the axes of the cube in multi-dimensional OLAP (MOLAP). It is typical in data warehousing and MOLAP to have the data sets be large and sparse, and it is not unusual in MOLAP data to find that 20% or fewer of the data elements are non-zero [42]. This degree of *sparsity* of data tends to be much higher with higher dimensions. We define the sparsity of a multi-dimensional array later in this text. Storing and manipulating large multi-dimensional data sets are also very common in many scientific and statistical databases, as well as scientific and engineering applications. The challenge in these applications is to find an efficient storage scheme to store very large data sets that have large number of dimensions.

## **1.1 Problem Motivation**

A typical representation of a multi-dimensional data model is as a multi-dimensional array. It organizes the data in multi-dimensional space, where each dimension represents one of the attributes of the data. The size of the multi-dimensional space is determined by the cross product of the cardinalities of each dimension. Such an approach is reasonably efficient when the array is dense, and has the advantage of excellent data access

efficiency. However, if the multi-dimensional data is sparse, using multi-dimensional array to represent such data sets requires extremely large data space while the actual data elements occupy only a small fraction of this space. Even though the entire storage space cannot be defined in memory, the actual data of non-zero values can be accommodated entirely in memory. Besides extremely large storage overhead, the efficiency in accessing data is easily traded off by visiting large amounts of invalid array elements. A number of storage schemes exist for sparse matrices, i.e., 2-dimensional sparse arrays, but not necessarily for higher dimensional arrays. Sparse matrices and sparse arrays result from data structures used for representing the information in various applications. Examples are: i.) use of adjacency matrix representation for very large graphs in numerous graph applications; ii.) multi-dimensional representation of relations for relational database and consequently in data warehousing.

The data in data warehousing and MOLAP is characterized by large volume, high dimensionality, and sparsity. Let  $\rho$  denote the *occupancy ratio* of a k-dimensional array  $A[D_{k-1}] \dots [D_0]$ , where  $D_j$ ,  $0 \le j \le k - 1$ , is the cardinality or bound of the  $j^{th}$  dimension. Suppose the number of non-zero elements is  $\mathcal{N}_{nz}$ , then  $\rho = \mathcal{N}_{nz} / \prod_{j=0}^{k-1} D_j$  and the sparsity , denoted by  $\sigma$ , is defined by  $\sigma = 1 - \rho$ . Multi-dimensional array is often a desirable data structure to be used to represent the data in data warehousing and MOLAP. It is essential to handle the sparsity in the array structure so that we can achieve overall performance enhancement. Efficient storage schemes of sparse matrices have been developed to gain significant performance improvements in scientific computing and engineering applications.

## **1.2 Problem Statement**

The question is whether a storage scheme can be implemented that stores only those occupied cells of array elements (or the non-zero values) in the corresponding multi-dimensional array structure with efficient element access performance. The problem we address concerns developing and implementing a storage scheme for multi-dimensional sparse arrays (MDSAs) that uses space proportional to the number of non-zero elements without compromising on the element access efficiency. Formally, we have the following: given a k-dimensional array  $A[D_{k-1}] \dots [D_1] [D_0]$  of  $\mathcal{N}_{nz}$  non-zero elements where  $\mathcal{N}_{nz} \ll \prod_{j=0}^{k-1} D_j$ , define an efficient representation of the array A using space  $O(\mathcal{N}_{nz})$  that has element access time of O(k) at best and  $O(\log \mathcal{N}_{nz})$  in the worst case. To elaborate on the problem statement, consider the non-zero elements of the k-dimensional sparse array,  $A[D_{k-1}] \dots [D_0]$  mapped onto a p-dimensional array  $F[M_{p-1}] \dots [M_0]$  where p < k. The size of F is  $\prod_{j=0}^{p-1} M_j = s \ge c \mathcal{N}_{nz}$ , for some small constant c. The array F is assumed to be linearized into a sequence of consecutive memory locations  $\mathcal{L}[s] = \mathcal{L}\langle 0 \rangle, \mathcal{L}\langle 1 \rangle, \dots, \mathcal{L}\langle s-1 \rangle$ . The problem then becomes finding a data structure to represent  $\mathcal{L}$  and a function f() that maps an element  $A\langle n_{k-1}, n_{k-2}, \dots, n_0 \rangle$

onto a location  $\mathcal{L}\langle q \rangle$ , with  $A\langle 0, 0, \dots, 0 \rangle$  assigned to  $\mathcal{L}\langle 0 \rangle$  such that  $\mathcal{L}$  stores only or mostly the non-zero elements. We desire an efficient compute function f() such that  $f(\langle n_{k-1}, n_{k-2}, \dots, n_0 \rangle) \to q$  and its inverse function  $f^{-1}(q) \to \langle n_{k-1}, n_{k-2}, \dots, n_0 \rangle$ .

Our primary goal in this research is to develop efficient storage schemes for multi-dimensional sparse arrays that address the problem stated above, i.e., reducing the storage overhead and maintaining the data access efficiency for query operations. Less storage overhead results in reduced memory and disk space, and better utilization of memory bandwidth. Efficient data access ensures less runtime penalties and faster matrix and array computations. It is also crucial to perform the typical array operations and data analytics on the result-ing data structure of any storage scheme without restoring the original sparse array. A number of problems precipitate from the original principle research problem. These include:

- Time to create the representative structure of  $\mathcal{L}$ : The general presentation of the non-zero elements of a sparse matrix or array is in the Matrix Market format (MM-format) [3, 4], which is also referred to as the *Coordinate* format. It is an ASCII file format with indexes that are either 0-based or 1-based. Each record gives the coordinates and the non-zero value. The first record represents the values of the bounds of the dimensions and the number of records of non-zero values in the file. Given an MDSA in the MM-format, the question is how fast can the data structure for  $\mathcal{L}$  be created? What is the occupancy ratio achievable by  $\mathcal{L}$ ?

- **Complexity of accessing a random element**  $A\langle n_{k-1}, \ldots, n_0 \rangle$ : Given the array index  $\langle n_{k-1}, \ldots, n_0 \rangle$ , what is the complexity of computing  $q = f(\langle n_{k-1}, \ldots, n_0 \rangle)$ , or given the value of q, what is the complexity of computing  $\langle n_{k-1}, \ldots, n_0 \rangle = f^{-1}(q)$ ?

- Sub-array retrieval: Given a k-dimensional array  $A[D_{k-1}] \dots [D_0]$  and rectilinear boundary indexes  $L = \langle l_{k-1}, \dots, l_0 \rangle$  and  $H = \langle h_{k-1}, \dots, h_0 \rangle$  where  $l_j \leq h_j, 0 \leq j \leq k-1$ , what is the time to return all the non-zero elements in the sub-array defined by L and H?

- **Multi-dimensional aggregation:** Given an aggregate function f() and a subset of k dimensions, how fast can the aggregation be computed for the representative data structure of  $\mathcal{L}$ ? This is also related to the problem of sub-array retrieval where in that case, an aggregate function is applied to the elements retrieved.

- Nearest neighbor retrieval and top-k: Given a non-zero value  $\mathcal{L}\langle q \rangle$  and a distance metric, determine the nearest non-zero element  $\mathcal{L}\langle q' \rangle$ . Related to this is the top-k that subsumes the nearest neighbor query. In this case we are given a non-zero value  $\mathcal{L}\langle q \rangle$  and a measure function g(), we desire the first k values  $\mathcal{L}\langle q'_1 \rangle, \mathcal{L}\langle q'_2 \rangle, \dots, \mathcal{L}\langle q'_k \rangle$ , closest to  $\mathcal{L}\langle q \rangle$  that satisfy  $g(\mathcal{L}\langle q \rangle) \otimes g(\mathcal{L}\langle q'_j \rangle), 1 \leq j \leq k$ , where  $\otimes \in \{<, \leq, =, >, \geq\}$ .

Multi-dimensional data model not only captures the structure of the underlying data well, it is also amenable to parallelism. Parallelism plays a significant role in processing the massive amount of data in data warehousing and MOLAP. As the secondary goal of this research, we explore parallelizing selected array operations on GPUs using some of the storage schemes concerned in this research. The selected array operations include large scale random array element access, sub-array retrieval, as well as multi-dimensional aggregation on a special case of the *cube* computation.

### **1.3 Overview of Some Known Approaches**

A number of methods have been used to handle sparse multi-dimensional arrays in the literature. In the case of 2-dimensional sparse arrays or sparse matrices the Compressed Row (or Column) Storage (CRS/CCS) is a well known scheme. This is discussed in detail in Section 2.1.4. The *Offset-Value* pair [51] is the most often used method to optimize the storage utilization of multi-dimensional sparse arrays with higher dimensionality (> 2). It stores only a pair of values; an offset value l and the data element v, for each non-zero element in the sparse array, given a scan order of the array and thereby incurring a low storage overhead. Some typical scan orders are the *row-major* or *column-major* order. Given a k-dimensional array  $A[D_{k-1}] \dots [D_0]$ , where an element  $A\langle n_{k-1}, \dots n_0 \rangle$ , is referenced by the indexes  $n_{k-1}, n_{k-2}, \dots, n_1, n_0$ , a scan order is termed *rowmajor* if the scan of the elements has the lowest index  $n_0$ , varying the fastest. It is termed *column-major* order if the high order index  $n_{k-1}$  varies the fastest. The computation of offsets from the array indexes, or vice versa, requires certain number of algebraic operations such as multiplication, addition, division, or subtraction. These computations become expensive when they are performed on a large number of dimensions.

Bit Encoded Sparse Storage (BESS) [12] was designed to overcome the computational cost of offset-value pair by encoding the array indexes into binary bits, concatenating these bits, and interpreting the concatenated bit string as an integer (see Section 2.1.3 for more details). As a result, the algebraic operations are replaced by more efficient bit concatenation operation. This method has the same storage efficiency as the offset-value pair. The random array element access time, in both cases, is achieved in time  $O(\log N_{nz})$ , since a binary search algorithm has to be used for a random element access.

Sparse matrices, a class of multi-dimensional array with k = 2, arise in a wide range of compute-extensive scientific and engineering applications. Many different storage schemes for sparse matrix have been designed to take advantage of the structure of the matrices or the specificity of the problem from which they arise. Consequently, these storage schemes are often application or structure specific, and limited to 2 dimensions. On the other hand, there are relatively much less methods to efficiently represent multi-dimensional sparse arrays of more than 2 dimensions. The k-dimensional data models applied in data warehousing, OLAP systems and multi-dimensional databases, typically have k > 2.

# **1.4 Overview of Our Solution**

We developed four storage schemes for MDSAs, and implemented algorithms for constructing these schemes. Our approaches, in developing new storage schemes, include extending sparse matrix storage schemes to higher dimensions, combining different storage schemes, and applying suitable data compression, when necessary, to the resulting representation of MDSAs using some storage formats. We also further explored a trie based approach, PATRICIA Trie Compressed Storage, an improved version from our previous work [48]. These storage schemes are:

- **Extended Compressed Row Storage (xCRS):** Compressed Row Storage, the widely used sparse matrix storage scheme, is extended to represent sparse arrays of any dimensions by simply mapping the multidimensional sparse array to a set of one dimensional arrays.

- **Bit Encoded Extended Compressed Row Storage (BxCRS):** To address the shortcoming of xCRS on very sparse multi-dimensional arrays, we applied data compression using Run Length Encoding to optimize the storage utilization of xCRS, while maintaining its data access efficiency.

- **Hybrid Approach (Hybrid):** The xCRS and BESS are combined to give a better control of the balance between storage utilization and data manipulation efficiency.

- **PATRICIA Trie Compressed Storage (PTCS):** A PATRICIA trie that stores a key-value pair for each nonzero element is constructed for a given MDSA.

To evaluate the storage schemes, we designed and implemented algorithms for *large scale random array element access*, *sub-array retrieval*, and *multi-dimensional aggregation*, for each of the storage schemes outlined in the previous paragraph, as well as a known scheme, BESS, for comparative purpose. As a special case of multi-dimensional aggregation, we also implemented algorithms to compute the *cube* operator using two storage schemes, namely PTCS and BESS, respectively.

We explored accelerating some of the operations for the sparse arrays using GPU as a co-processor. These operations include large scale random array element access or searching, and sub-array retrieval. Finally, computing the *cube* operator using BESS was accelerated using GPU as a co-processor. Data warehousing and OLAP analyze large volumes of data and are highly compute- and data-intensive. In addition, the multi-core

and many-core architectures are the current predominant technologies and will remain as trends in the future. Therefore, parallelism should be exploited whenever possible in these applications. We chose GPU as the parallel platform for this purpose. Traditionally designed for gaming applications, GPUs have relatively more computing power and high memory bandwidth compared with their contemporary CPUs. While the performance of graphics hardware is rapidly increasing, they become more programmable due to the flexible architectural designs with every major generations of GPUs. High level GPU programming models and languages, or programming models for heterogeneous systems, such as Compute Unified Device Architecture (CUDA) from NVIDIA [32] and OpenCL [23], have been emerging to meet the demands of utilizing GPUs or other types of processors for general purpose computing. Furthermore, compared with other parallel platforms, heterogeneous systems often have potential to achieve excellent *performance/cost* ratio. All these features of GPUs make them an attractive platform to be utilized in many applications. Recent research work has shown that GPUs can be used to accelerate data warehousing applications [49, 46]. GPUs have been successfully applied to accelerate individual database operations, such as sort [13] and join [19], relational query processing [18], and some of the data mining operations [11].

As part of the work of our second goal, the issue of computing the multi-dimensional aggregation on a special case of the *cube* operator was examined. The *cube* operator is the multi-dimensional generalization of *group-by* [44] operator. It computes group-bys corresponding to all possible combinations of a list of attributes. Many queries over data warehouses and MOLAP require summary data and as such use aggregate operations. Further, data analyses in these applications are often interactive. Hence, response time is a crucial factor in the performance. Materializing some of the summary data, or pre-computing partial or total *cube*, is a key technique to answer common queries efficiently in data warehousing and MOLAP. In computing the *cube*, we mainly combined the following two approaches; one was to represent the MDSA using a space efficient storage scheme, such as BESS; the other was to utilize GPUs in computing some part of the cube operation.

Taking the time constraint into consideration, we restricted ourselves to consider only the case where the data can be fit into main memory, leaving the case where the data can not fit into main memory for future work. The methods to represent MDSAs we propose ensure either more data fitting into main memory or efficient access to the data. Accommodating more data in main memory results in less partitioning cost on disk data, hence less I/O cost. Graefe pointed out a number of benefits of data compression in database system [14]. These benefits include reduced disk space, improved I/O performance, more data being fit into main memory, etc. The author also pointed out that most query processing can be carried out on the compressed data. Some of these benefits can be realized to a certain degree by applying a suitable storage scheme to an MDSA. Organizing MDSAs using an efficient storage scheme could lead to two fold benefits. Firstly, we may achieve an optimal storage utilization, efficiency in data manipulation, or a desired balance between them, by carefully choosing a storage scheme to represent the MDSA. Secondly, we may further apply one of the data compression techniques, such

as in the case of BxCRS, to the data represented in some storage schemes to improve the storage utilizations while maintaining their data access efficiencies.

# **1.5 Main Contributions**

The main contributions of this dissertation include the following. Firstly, we designed, implemented and evaluated four of the storage schemes for MDSAs, namely xCRS, BxCRS, Hybrid and PTCS. These methods contribute towards a wider range of methods of organizing MDSAs in data warehousing, MOLAP, and other relevant applications in different fields. They provide different features such as optimal storage utilization, efficient data access, or some balance between the two. Among these methods, we investigated various basic yet novel ideas, such as using trie based data structure to store MDSAs, combining different storage schemes to gain better control of the balance between space and computational efficiencies, and applying data compression within a storage scheme. Secondly, by utilizing GPUs as a co-processor to accelerate some selected array operations, we demonstrated how GPUs can be applied to accelerate some basic operations in data warehousing and MOLAP, and consequenly improve the performance in these applications. Thirdly, we implemented computing the *cube* using BESS as the storage scheme, and utilizing GPUs as the co-processor. The benefits of this approach are as follows.

- Using BESS as the storage scheme leads to more data being accommodated in memory. Further, since BESS represents the dimensional data (or the indexes of the array elements) in a very compact form, it not only simplifies some of the necessary operations, such as sorting when computing the *cube*, but also optimizes the PCI-Express bus bandwidth between the CPU and GPU implicitly, by transferring more information in the same amount of data.

- We were able to achieve a speed-up of 5 to 8 times compared with our single-core CPU implementation of computing the *cube* using BESS or PTCS. Hence, the effectiveness of utilizing both CPU and GPUs on the problem of computing the *cube* was demonstrated.

Due to the limited time for this research, the problems of nearest neighbor and top-k retrievals are not addressed in this dissertation. They are left for future work, where we hope to design and implement the algorithms in these regards for the data represented by the selected storage schemes.

# **1.6 Organization of the Dissertation**

The rest of this dissertation is organized as follows. Chapter 2 gives the backgrounds and related works in MDSA storage schemes, data warehousing and OLAP, multi-dimensional aggregation and general purpose computing on GPUs. We introduce the designs of new storage schemes in Chapter 3, as well as the relevant algorithms for creating the storage structures, implementing the basic array operations, and give some analytical properties of each scheme. We discuss computing the multi-dimensional aggregations and the *cube* operator using various storage schemes in Chapter 4. Our approaches to utilize GPUs on the selected array operations are presented in Chapter 5. The experimental setup and discussion of data sources for reproducibility are given in Chapter 6. The experimental results and comparative analyses of the results obtained are presented in Chapter 7. We finally conclude the work of this dissertation in Chapter 8, where we also discuss the direction for future work.

# Chapter 2

# **Background and Related Work**

In this chapter, we discuss related work on multi-dimensional sparse array representation and their application to data warehousing and OLAP. We discuss earlier works on computing multi-dimensional aggregates and the *cube* operator. We also briefly present the GPU architecture, the CUDA programming model and their use as general purpose computing engines in related fields.

## 2.1 Storage Schemes for Multi-Dimensional Sparse Arrays

There exist a number of storage schemes for multi-dimensional sparse arrays, mostly specialized for sparse matrices. Many different schemes for sparse matrices have been designed to take advantage of the structure of the matrices or the specificity of the problem from which they arise. For example, the special sparse structures that are often exploited in designing storage schemes for sparse matrix include: a diagonal matrix where the matrix consists of a few diagonals of non-zero elements; a block matrix where the non-zero elements are square dense blocks; symmetric matrix; asymmetric matrix etc. The purpose of each of these schemes is to gain efficiency both in memory utilization and matrix computations. A survey of such a collection of sparse matrix storage formats can be found in the work of Barret et al. [2] and Saad [39].

In the following text, we give an overview of some of the known storage formats that are relevant to our work. These formats are general in the sense that they do not make any assumption about the sparsity or the structural shape of the underlying arrays. Table 2.1 gives the notations and descriptions of the parameters used in the analyses of the various storage schemes in this dissertation.

| Parameter<br>and Notation | Description                                                                         |

|---------------------------|-------------------------------------------------------------------------------------|

| $C_i$                     | The number of bytes in an integer                                                   |

| $C_{il}$                  | The number of bytes in the longest integer                                          |

| $C_f$                     | The number of bytes in a float or real number                                       |

| $d_j$                     | The name of a dimension $j$                                                         |

| $D_j$                     | The cardinality or bound of a dimension $j$ or $d_j$                                |

| S                         | The size of a storage space in bytes                                                |

| W                         | The bit length of a computer word                                                   |

| $\mathcal{N}_{nz}$        | The number of non-zero elements in an array                                         |

| $\mathcal{N}_{j}$         | $\mathcal{N}_j = \prod_{r=k-j}^{k-1} D_r, 1 \le j \le k$                            |

| ρ                         | The occupancy ratio, $ ho = \mathcal{N}_{nz}/\mathcal{N}_k$                         |

| σ                         | The sparsity of an MDSA, $\sigma = 1 - \rho$                                        |

| l, v                      | The offset and value pair for an array element $A\langle n_{k-1} \dots n_0 \rangle$ |

| BEI                       | Bit Encoded Index                                                                   |

Table 2.1: The parameters and notations

### 2.1.1 Index-Value Pair

The index-value pair format is the simplest format for representing an MDSA. It is also termed Coordinate (COO) format and is commonly used for sparse matrices. This is the general format for storing the non-zero values of an MDSA in an ASCII file and is also referred to as the Matrix-Market format [3]. To represent a k-dimensional sparse array, the index-value pair uses k + 1 one-dimensional arrays or vectors; one vector for storing all the non-zero values, and the other k vectors for storing the indexes of the corresponding non-zero values. The length of each of these vectors is  $\mathcal{N}_{nz}$ , i.e., the number of non-zero elements. Hence, the total storage space required for the index-value representation is  $(kC_i + C_f)\mathcal{N}_{nz}$ . Table 2.2 shows the index-value pair representation of an example MDSA in Figure 2.1. In Table 2.2, the vector *val* stores the non-zero values, and the vectors *ind*1, *ind*2, *ind*3 store the corresponding indexes, for each non-zero value, on dimension I, J, K respectively. The example of the 3-dimensional sparse array of Figure 2.1 is used throughout the dissertation.

Both the storage and the data access efficiencies of the index-value pair format become worse when the number of dimensions, k, increases. However, two variations to this format, namely, Offset-Value Pair and Bit Encoded Sparse Storage, are commonly applied for MDSAs of higher dimensions, where the k one-dimensional arrays of indexes are reduced to only one.

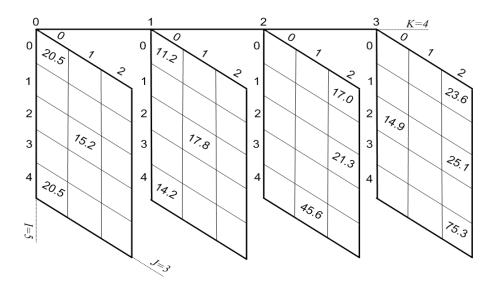

Figure 2.1: An example 3-dimensional  $(5 \times 3 \times 4)$  sparse array.

| ind1 | ind2 | ind3 | val  |

|------|------|------|------|

| 0    | 0    | 0    | 20.5 |

| 0    | 0    | 1    | 11.2 |

| 0    | 2    | 2    | 17.0 |

| 0    | 2    | 3    | 23.6 |

| 2    | 0    | 3    | 14.9 |

Table 2.2: The index-value pair representation of the MDSA in Figure 2.1.

### 2.1.2 Offset-Value Pair

Given a k-dimensional sparse array  $A[D_{k-1}] \dots [D_0]$ , the offset-value pair format represents each non-zero element in A using two values, an offset and the non-zero value. The offset l is a displacement in a given linearly addressed space starting from 0. We may obtain a linear address space for any sparse array by traversing the array elements in a certain scan order, such as *row-* or *column-major* order. Other scan orders are the *Z-order*, the *Peano-Hilbert order* and the *Grey-Code* order [40]. For example in a *row-major* offset-value representation, the k-dimensional index  $\langle n_{k-1}, \dots, n_0 \rangle$  of any array element is used to compute its offset l as

$$l = \sum_{i=0}^{k-1} n_i \prod_{j=0}^{i-1} D_j$$

Offset-value pair storage uses two one-dimensional arrays; one to store the actual non-zero values and the other to store the corresponding offsets. The lengths of both of these two arrays are  $\mathcal{N}_{nz}$ . Thus, the storage space requirement using offset-value pair is only  $(C_{il}+C_f)\mathcal{N}_{nz}$ . Table 2.3 shows two offset-value pair representations of the 3-dimensional array of Figure 2.1 for two different linear addressing. This method is often used to represent multi-dimensional sparse arrays because of its storage efficiency [51], which is linear in the number of non-zero elements. Random array element access in offset-value pair has a complexity of  $O(\log N_{nz})$ using *binary search*. One may argue if the use of interpolation search, with average search time complexity of  $O(\log \log N_{nz})$  [37], would not be more appropriate. In practice, this is worse than the use of binary search, since the interpolation search involves multiplication and division of floating point numbers while the binary search involves only one integer division by 2 and is more efficient.

| val  |                                      | $offset_2$                           | val                                                   |

|------|--------------------------------------|--------------------------------------|-------------------------------------------------------|

| 20.5 |                                      | 0                                    | 20.5                                                  |

| 11.2 |                                      | 4                                    | 20.5                                                  |

| 17.0 |                                      | 7                                    | 15.2                                                  |

| 23.6 |                                      | 15                                   | 11.2                                                  |

| 14.9 |                                      | 19                                   | 14.2                                                  |

| 15.2 |                                      | 22                                   | 17.8                                                  |

|      |                                      |                                      |                                                       |

|      |                                      | В                                    |                                                       |

|      | 20.5<br>11.2<br>17.0<br>23.6<br>14.9 | 20.5<br>11.2<br>17.0<br>23.6<br>14.9 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

Table 2.3: The offset-value pair representations of the MDSA in Figure 2.1. Table A is in the row-major (I - J - K) order, and Table B is in the column-major (K - J - I) order.

The major shortcoming of offset-value pair is that it is not computationally efficient. To compute an offset, we need to do k - 1 multiplications and summations, and to recover the array index, we need to do the same amount of divisions and subtractions. Another issue of offset-value pair is that it has the potential to overflow. The value  $\prod_{i=0}^{k-1} D_i$  tends to be very large when the dimensionality increases, or the individual dimensions have large cardinalities. This could result in a large integer value that overflows the 32-bit or even a 64-bit integer representation. Our approach, in this dissertation, is to partition the very large linear address space, if it occurs, into relatively smaller ones.

### 2.1.3 Bit Encoded Sparse Storage

Bit Encoded Sparse Storage (BESS) consists of two one-dimensional arrays; one stores the non-zero values, the other stores the *bit encoded indexes* of the corresponding non-zero values [12]. This is very much like the Offset-Value pair approach, except that the 'Offset' in BESS is computed by concatenating the bit encoded representations of the indexes. Let  $\langle n_{k-1}, \ldots, n_1, n_0 \rangle$ , denote the index of a non-zero array element and let  $\beta_j, 0 \leq j < k$ , denote the compact binary bit representation of the index value  $n_j$ . A Bit Encoded Index (BEI) of such an array element is the integer representation of the concatenation of the  $\beta_j$ 's,  $\beta = \beta_{k-1} ||\beta_{k-2}|| \dots ||\beta_0|$ . The *BEI* is then interpreted as a simple integer position code. This can be perceived as the equivalent to the offset index in the preceding discussion of the *Offset-Value* representation. We term the generated *BEI* also as a *key*. An example of using BESS to represent the MDSA of Figure 2.1 is shown in Table 2.4. The column  $\beta$  is the concatenated bit sequences of the 3 index values for each non-zero element. We use  $\lceil \log D_i \rceil (0 \le i \le 2)$  bits for each dimension. These are concatenated in the order of I - J - K. The storage requirement of BESS is  $(C_{il} + C_f)\mathcal{N}_{nz}$ . A random array element is accessed in time  $O(\log \mathcal{N}_{nz})$ , since like the offset-value pair format, a binary search is used to determine whether a non-zero value exists or not given a *k*-dimensional index  $\langle n_{k-1}, \dots, n_1, n_0 \rangle$ .

| β        | BEI | val  |

|----------|-----|------|

| 00000000 | 0   | 20.5 |

| 00000001 | 1   | 11.2 |

| 00001010 | 10  | 17.0 |

| 00001011 | 11  | 23.6 |

| 00100011 | 35  | 14.9 |

| 00100100 | 36  | 15.2 |

|          |     |      |

Table 2.4: The BESS representation of the MDSA in Figure 2.1.

Offset-value pair and BESS are both very efficient in storage space utilization. However, the computational efficiencies of these two storage schemes are limited to using binary search or sequential scan of the nonzero values. The difference between them lies in the computation of the offset in the former and the BEI in the latter. While computing the offset of an array element involves certain number of multiplications and additions, constructing the BEI only takes a number of bit operations, which are considered to be more efficient than the arithmetic operations. A well studied comparison between the offset-value pair and BESS was presented in the work of Goil et al. [12] and the result showed that BESS is much more efficient than the the use of the offset-value pair. As a result, we compare our new methods being introduced in this dissertation, with BESS, but the basic idea of offset-value pair is applied in designing the methods of xCRS and the Hybrid storage scheme.

### 2.1.4 Compressed Row or Column Storage

Compressed row or column storage (CRS or CCS) is widely used to represent sparse matrices. It uses three one-dimensional arrays, denoted by *val*, *cind* and *rptr* respectively here, to represent a sparse matrix. The array *val* stores the non-zero values, *cind* stores the column indexes of each non-zero element and *rptr* stores

the pointers (position index of the values) of the starting position of each row in the array *cind*. Table 2.5 illustrates an example of CRS representation of a  $6 \times 6$  matrix A. In CRS, the array elements are traversed in row-major order. CCS is similar to CRS except that the array elements are traversed in column-major order. The random array element access time in CRS is  $O(\log D_0)$ . However, the actual sizes of the rows vary and can be far less than the cardinality  $D_0$  due to the sparsity of the matrix. Retrieval of a row is much more efficient than of a column in CRS, and vice versa in CCS.

|     | ( 10.2                                                                | 0    | 0    | 0    | 2.34 | 0    |

|-----|-----------------------------------------------------------------------|------|------|------|------|------|

|     | 13.7                                                                  | 23.5 | 0    | 0    | 0    | 11.6 |

| 4 — | 0                                                                     | 17.3 | 0    | 35.4 | 0    | 0    |

| л — | 53.2                                                                  | 0    | 28.1 | 0    | 0    | 0    |

|     | 0                                                                     | 0    | 0    | 89.4 | 0    | 13.9 |

|     | $ \begin{pmatrix} 10.2 \\ 13.7 \\ 0 \\ 53.2 \\ 0 \\ 0 \end{pmatrix} $ | 44.5 | 0    | 0    | 20.9 | 0 /  |

| offset | 0    | 1    | 2    | 3    | 4    | 5    | 6    | <br>10   | 11   | 12   | 13 |

|--------|------|------|------|------|------|------|------|----------|------|------|----|

| val    | 10.2 | 2.34 | 13.7 | 23.5 | 11.6 | 17.3 | 35.4 | <br>13.9 | 44.5 | 20.9 | 13 |

| cind   | 0    | 4    | 0    | 1    | 5    | 1    | 3    | <br>5    | 1    | 4    | 13 |

| rptr   | 0    | 2    | 5    | 7    | 9    | 11   | 13   |          |      |      |    |

Table 2.5: The CRS of matrix A

## 2.2 Data Warehousing and OLAP

The multi-dimensional data model, which we focus on in this research, is intended to represent primarily the data in data warehousing and OLAP. Data warehousing and OLAP are the core technology in decision support systems. Data warehousing refers to a collection of decision support technologies. It aim at enabling the knowledge workers to make better and faster decisions [5]. Data warehousing has been increasingly deployed in many industries, such as manufacturing, retail, financial services, etc. A data warehouse is an integrated repository that stores information which may originate from multiple, possibly heterogeneous operational or legacy data sources [41]. A data warehouse may contain original raw data or preprocessed data. OLAP, which enables analysts to work with data warehouses interactively, supports dynamic synthesis, analysis, and consolidation of large volumes of data [30].

The data in a warehouse and OLAP system is typically modeled as multi-dimensional data, in the sense that the data can be modeled as dimension attributes and measure attributes [44]. A measure attribute measures some numeric value, such as sales, budget, etc., and dimension attributes define the dimensions on which the

measures are viewed, such as time, location, etc. Thus, the multi-dimensional data views the measures as values in the multi-dimensional space. Further, a dimension can be defined by a set of attributes, forming a hierarchy. For simplicity, we did not take the hierarchy of a dimension into consideration in this research.

The construction, operation, and maintenance of a data warehouse and OLAP server involve many techniques and research issues. An overview of these topics is presented in the work of Chaudhuri et al. [5]. In the evaluations of the new and existing storage schemes, we selected four operations, namely the construction of the storage structure, random element access, sub-array retrieval and multi-dimensional aggregation, as the main performance criteria for comparisons. The random element access and sub-array retrieval are the most basic and yet fundamental operations to constitute the efficient queries over data warehouse, together with the slicing and dicing operations in OLAP. In the materialized views of data warehousing, roll-up and drill-down operations in OLAP use aggregations.

If the data in data warehouses and OLAP is to be represented in an MDSA storage format, the first basic array operation we need to consider is random element access. Data warehouses usually contain large volumes of data that are still sparse in the multi-dimensional space. It is essential to be able to efficiently access the data in order to answer the queries efficiently. Random element access, on one hand, means retrieving the value associated with a given array index. In array structure representation, this could be done conveniently by finding the displacement in a linear address space according to the index. However, when the array is represented in a certain storage scheme, to access an array element using its array index requires using computations according to the schemes. On the other hand, we may need to recover the array indexes of the elements given a position index in a storage scheme. The efficiency of this inverse mapping is actually a critical factor in the performance of computations, such as sub-array retrieval, aggregation, and nearest neighbor queries.

Unlike in operational databases, the operations in data warehousing and OLAP may not often access individual data; instead they often need to access the data in a 'sub-region'. For example, in Figure 2.1, we may only be interested in the data on the dimension I with index value 1 or 2. In this case, we need to extract the data on this specific dimension value efficiently. We refer to this operation as sub-array retrieval. More precisely, given a k-dimensional array  $A[D_{k-1}] \dots [D_0]$  and rectilinear boundary indexes  $L = \langle l_{k-1}, \dots, l_0 \rangle$  and  $H = \langle h_{k-1}, \dots, h_0 \rangle$  where  $l_j \leq h_j, 0 \leq j \leq k-1$ , we are required to retrieve all the non-zero elements in the sub-array defined by L and H. Sub-array retrieval constitutes the partial and exact match queries over data warehouses.

To analyze the multi-dimensional data in a data warehouse or MOLAP, an analyst may want to see a summary data in a number of selected dimensions. The summary data is often presented in an *m*-dimensional array  $(1 \le m \le k, k \text{ is the dimensionality})$ . Especially, in OLAP, the summary data is often called *cross-tab* or

*pivot-table* when m = 2, and *data cube* when m > 2. For example, in Figure 2.2, the aggregation result on the dimensions (J, K) is a *cross-tab*, the aggregation may also be carried on (I, K) or (I, J). These operations, called *pivoting*, are to get different summarized data by aggregating on some of the specific dimensions only, ignoring all the other dimensions, or assuming the special *all* [44] value for them. On the other hand, sometimes we assign fixed values, instead of the *all* value, on some dimensions first, then carry out aggregations on the remaining dimensions. We refer to these operations as *slicing* (specify a fixed value on one dimension only), and *dicing* (specify fixed values on more than one dimension). Besides these operations, OLAP servers also support two other operations, namely *roll-up* and *drill-down*. *Roll-up* refers to the aggregation operations that move from aggregating on more detailed group-by attributes to less detailed ones. *Drill-down*, the inverse of *roll-up*, refers to the aggregation operations that move from less detailed group-by attributes to more detailed ones. The typical OLAP operations we discussed above mainly involve aggregations on varying dimensions or combinations of dimensions, as well as accessing the data frequently on varying parts.

Refreshing or updating a data warehouse raises a number of issues in itself, although we do not consider them in this research. However, we should point out that among the storage schemes we considered, PATRICIA trie compressed storage (PTCS) has the unique advantage of efficiently supporting some update operations, such as insertion and deletion. This is due to the fact that PTCS employs PATRICIA trie structure to store the valid elements in an MDSA. The other storage schemes are based on array structure, where the insertion or deletion of a single element may cause the whole structure to be rebuilt.

### 2.3 Multi-Dimensional Aggregation

Aggregation is a very important statistical concept to summarize information about large amounts of data [14]. The idea is to represent a set of items by a single value or to classify items into groups and determine one value per group. Aggregation is usually supported in the form of *aggregate functions*, which determine a set of values from an input set of values, such as a relation. Aggregate functions can be classified into three categories: *distributive, algebraic* and *holistic* [16, 1]. An aggregate function f() is distributive if it allows the input data set to be partitioned into disjoint sets that can be aggregated independently and the results combined to obtain the final one. Aggregate functions such as determining the maximum, minimum, summation, count of values, are all distributive. Algebraic aggregate functions, such as computing the average value, can be expressed in terms of other distributive functions. Holistic aggregate functions, such as finding the median or standard deviation, are those that cannot be computed in parts and combined. Aggregation is an important operation in data warehousing and MOLAP applications typically aggregate data across many dimensions, when

processing queries or looking for anomalies, patterns and trends.

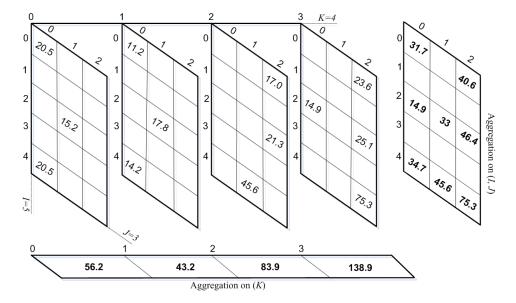

The group of attributes constituting the dimensions along which the aggregates are computed are called the *group-by* attributes or dimensions. Since we do not consider the hierarchy of a single dimension in this research, we use the term dimension and attribute interchangeably. The Figure 2.2 shows the aggregations on the group-bys of a single dimension (K) and two dimensions (I, J) for the MDSA in Figure 2.1. The aggregate function in this example is *summation*. For example, to compute the aggregation on the group-by of K, we group the array elements according to their index value on dimension K. Those elements with the same index value on k are grouped into the same group. The aggregate function is then carried on to each group. Figure 2.3 shows this process. Given a k-dimensional sparse array, aggregating on a group of  $m(1 \le m \le k)$  dimensions results in an m-dimensional array. Algorithms for aggregate functions require grouping of the input data, and then one output item is computed per group. The typical grouping methods are based on either *sorting* or *hashing*.

Figure 2.2: The aggregations with the aggregate function as summation, on a single dimension and multiple dimensions

### 2.3.1 The CUBE

It is often necessary to aggregate data efficiently in data warehousing applications. To make interactive analysis possible in these applications, various levels of aggregations are usually precomputed. To conveniently support multiple aggregations, Gray et al. proposed the "*cube*" operator [16], which computes aggregations over all possible combinations of a set of dimensions. By changing the granularity on the group of attributes or dimensions, different aggregation information can be obtained. For example, to analyze computer sales, one might put special focus on the effects of brand and type of the computers, ignoring all the other attributes. In such a

| к | J | 1 | val  | sum(val) |  |

|---|---|---|------|----------|--|

| 0 | 0 | 0 | 20.5 |          |  |

| 0 | 0 | 4 | 20.5 | 56.2     |  |

| 0 | 1 | 2 | 15.2 |          |  |

| 1 | 0 | 0 | 11.2 |          |  |

| 1 | 0 | 4 | 14.2 | 43.2     |  |

| 1 | 1 | 2 | 17.8 |          |  |

| 2 | 1 | 4 | 45.6 |          |  |

| 2 | 2 | 0 | 17.0 | 83.9     |  |

| 2 | 2 | 2 | 21.3 |          |  |

| 3 | 0 | 2 | 14.9 |          |  |

| 3 | 2 | 0 | 23.6 | 138.9    |  |

| 3 | 2 | 2 | 25.1 |          |  |

| 3 | 2 | 4 | 75.3 |          |  |

|   |   |   |      |          |  |

Figure 2.3: The aggregation process for the group-by of a single dimension K. The aggregate function is summation.

case, we may analyze the total sale of computers by brand and type respectively, or by some combinations of both. Given a data set with k attributes, the number of all possible combinations of the k attributes is  $\sum_{i=0}^{k} {k \choose i}$ , which is  $2^k$ . This number is exponential with respect to the number of dimensions. Thus, computing the *cube* presents challenges on both speed and space.

A number of efficient methods of computing multi-dimensional aggregation and the *cube* have been developed [1, 38, 51, 17]. While many of these methods have been developed in the context of relational database systems, most of them are applicable to the database systems with different data models. In the following text, some of the basic rules in computing aggregation and the *cube* are outlined, we also present some of the state of the art methods in computing the *cube*.

As Graefe points out in [14], two types of algorithms for aggregation, based on sorting and hashing are often used in standard database aggregation problems. The data items are sorted on their grouping attributes in a sort-based aggregation algorithm. This allows us to compute multiple aggregations in one scan of the data. Furthermore, the output data is also in sorted order and can further be exploited to compute other aggregations. By hashing on the grouping attributes, items of the same group can be found and aggregated in hash-based algorithms.

Some basic techniques for computing the *cube* are outlined in the work of Gray et al. [16]. The objectives of these techniques are to:

- Minimize the data movement.

- Use sorting or hashing to organize the data.

- Map the non-integer types of attribute values to integers starts from zero.

- Use parallelism.

#### 2.3.1.1 Search Lattice

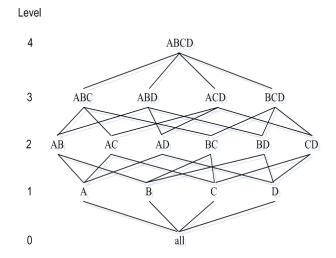

Underlying all the *cube* construction methods for relational data sets is the lattice representation of  $2^k$  combinations of k attributes and their parent-child relationships. Such a lattice for 4 attributes (dimensions) is shown in Figure 2.4. Each node, called a *cuboid*, in the lattice represents some combination of the attributes and the *all*

Figure 2.4: A search lattice with 4 attributes.

node represents the empty combination. The edges represent the parent-child relationships between the nodes. There is an edge connecting two nodes if one (child) of them can be computed from the result of the another (parent). For example, the edge between ABC and AB indicates the aggregation on AB can be computed from the result of the aggregation on ABC. Figure 2.4 shows that at each level, a child node may have more than one parent node from which it can be computed. It is necessary to find the parent that minimizes the cost of computing the child node. The algorithm presented in the work of Agarwal et al. [1] found the best way of computing each level  $i^{-1}$  from level i + 1 by reducing the problem to a weighted bipartite matching problem. Once each child node is assigned to a parent, the search lattice can be partitioned into a number of paths each containing a series of cuboids with parent-child relationships determined. For example, in Figure 2.4, one such

<sup>&</sup>lt;sup>1</sup>Typically, the *all* node in a search lattice is at level 0, and level i includes all the cuboids with the combinations (group-bys) of i attributes.

path is  $ABCD \rightarrow ABC \rightarrow AB \rightarrow A$ . To compute all the group-bys on this path, the input data need to be sorted only once according to the attribute order at the root node (node ABCD in this case), and read only once as well. In order to optimize the *cube* computation, it is often desirable to determine a certain number of paths in the search lattice so that the cost of sorting, memory space requirement and disk reads, of computing the *cube* can be minimized. Ross et al. in [38] argued that there must exist at least  $\binom{k}{\lfloor k/2 \rfloor}$  paths in the search lattice. They also showed that this was an upper bound on the number of paths required to cover all the nodes in the search lattice. The algorithm to find  $\binom{k}{\lfloor k/2 \rfloor}$  paths proposed in [38] is further discussed in Chapter 4.

Based on the different approaches to utilize parent-child relationships among the nodes in the search lattice, two methods, top-down and bottom-up, are often used to compute the *cube*. Top-down approach computes less detailed group-bys from more detailed ones, so that one sort operation at the finest level granularities may be shared among the less detailed ones. Bottom-up approach computes more detailed group-bys from less detailed ones so that the partial sort on the less detailed granularities may be used to generate more detailed sorts.

#### 2.3.1.2 Algorithms for Computing the CUBE

Fast algorithms to compute the *cube* operator were introduced in [1] by optimizing sort-based and hash-based grouping methods with several optimizations. These optimization techniques include:

- 1. Combining common operations across multiple aggregates;

- 2. Caching the results of a group-by from which other group-bys are computed;

- 3. Computing as many group-bys as possible while the input data is in memory and sorted in a certain attribute order;

- 4. Sharing sorting cost in sort-based methods or partitioning cost in hash-based methods across multiple group-bys.

The algorithm *PipeSort* [1], first generates a set of paths using a local optimizing technique based on weighted bipartite matching at each level of the search lattice. These paths are then evaluated in turn. During the evaluation of a path, the data is sorted in the order indicated by the attribute order of the root node in the path. After the data is sorted, all the group-bys in the path are computed in pipelined fashion during a single scan of the data. The number of sorts that *PipeSort* has to perform, is at least  $\binom{k}{\lceil k/2 \rceil}$ , which is exponential in *k*, the number of dimensions. Clearly, when the number of dimensions increases, the cost of sorting will dominate the

complexity of the *cube* computation. Thus parallelism of the sort operation, which we will show in Chapter 5, is a viable means to improve the efficiency of computing the *cube*.

The algorithm *Memory-Cube*, introduced in [38], is similar to *PipeSort* in that it also applies the pipelined evaluation of the cuboids in a path. However, *Memory-Cube* tries to generate an optimal set of paths (i.e., the number of sorts) in the search lattice while *PipeSort* does not guarantee this. Further, *Memory-Cube* utilizes considerably sharing of the cost of sorts among different paths.

An array-based algorithm, *Array-Cubing* algorithm, to compute the *cube* for MOLAP systems introduced by Zhao et al. [51] performs well because the array representation allows direct access to the data elements. Most importantly, re-sorting the non-zero values on different sets of aggregate attributes can be done by simply visiting those array elements in the right order. It was also shown that given appropriate data compression techniques, the *Array-Cubing* algorithm could be significantly faster than the relational algorithms, and it might also be used for relational OLAP. Array-Cubing algorithm organizes large arrays in chunks, and the array chunks in turn are organized using offset-value pair storage scheme. The algorithm computes a minimum memory spanning tree (MMST) for a given dimension order, based on the choice of the parent node that minimizes the memory required for computing a child node at each level. Generally, if the required memory for each MMST node is allocated, the computation of the nodes can be done concurrently. However, this is not always the case for large sparse data sets with high dimensions.